Table 2–5, Table 2–6 – Altera SDI HSMC User Manual

Page 17

Chapter 2: Board Components

2–9

Clock Circuitry

© July 2009 Altera Corporation

lists the second frequency translation stage of the SDI multi-frequency

VCXO femto clock video PLL.

shows the bypass function of the SDI multi-frequency VCXO femto clock

video PLL.

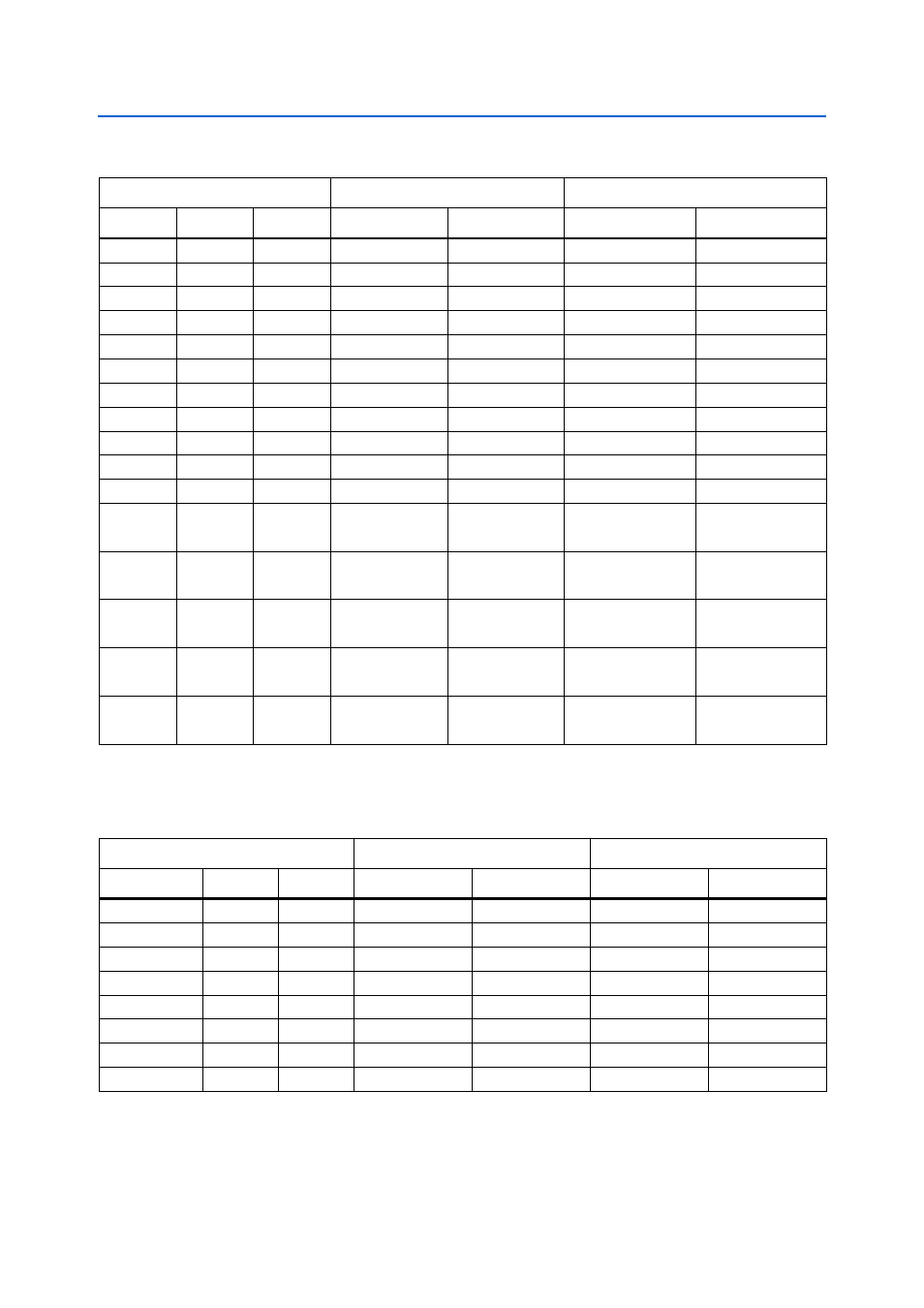

Table 2–5. First Frequency Translation Stage of the SDI Multi-Frequency VCXO Femto Clock Video PLL

VCXO PLL Divider Look-Up Table

Video Clock Application

Alternate Video Clock Application

V3:V0 Pins

P Value

M Value

Input

VCXO

Input

VCXO

0000

1000

1000

27 MHz

27 MHz

26.973 MHz

26.973 MHz

0010

1001

1000

27 MHz

26.973 MHz

—

—

0010

11000

4004

74.175 MHz

27 MHz

—

—

0011

11011

4000

74.25 MHz

26.973 MHz

—

—

0100

11000

4000

74.25 MHz

27 MHz

—

—

0101

4004

4004

27 MHz

27 MHz

26.973 MHz

26.973 MHz

0110

4004

4000

27 MHz

26.973 MHz

—

—

0111

1000

1001

26.973 MHz

27 MHz

—

—

1000

250

91

74.175 MHz

27 MHz

—

—

1001

253

92

74.25 MHz

27 MHz

—

—

1010

92

92

27 MHz

27 MHz

26.973 MHz

26.973 MHz

1011

1

600

45 kHz

(720P/60 hsync)

27 MHz

44.955 kHz

(720P/59.94)

26.973 MHz

1100

1

800

33.75 kHz

(1080l/60 hsync)

27 MHz

33.716 kHz

(1080l/59.94)

26.973 MHz

1101

1

1728

15.625 kHz

(PAL hsync)

27 MHz

—

—

1110

1

1716

15.734 kHz

(NTSC hsync)

27 MHz

—

—

1111

1

960

28.125 kHz

(1080l/50 hsync)

27 MHz

—

—

Table 2–6. Second Frequency Translation Stage of the SDI Multi-Frequency VCXO Femto Clock Video PLL

Femto Clock Look-Up Table

Video Clock Application

Alternate Video Clock Application

MF, N1:N0 Pins

FB Div

Out Div

VCXO

Q

VCXO

Q

0,00

22

4

27 MHz

148.5 MHz

26.973 MHz

148.35 MHz

0,01

22

8

27 MHz

74.25 MHz

26.973 MHz

74.175 MHz

0,10

22

12

—

—

—

—

0,11

22

18

—

—

—

—

1,00

24

4

—

—

—

—

1,01

24

8

—

—

—

—

1,10

24

12

27 MHz

54 MHz

—

—

1,11

24

18

27 MHz

36 MHz

—

—