Configuring the cyclone ii fpga, Jtag programming, Configuring the cyclone ii fpga –3 – Altera Cyclone II FPGA Starter Development Board User Manual

Page 11

Altera Corporation

Reference Manual

1–3

October 2006

Cyclone II FPGA Starter Development Board

Introduction

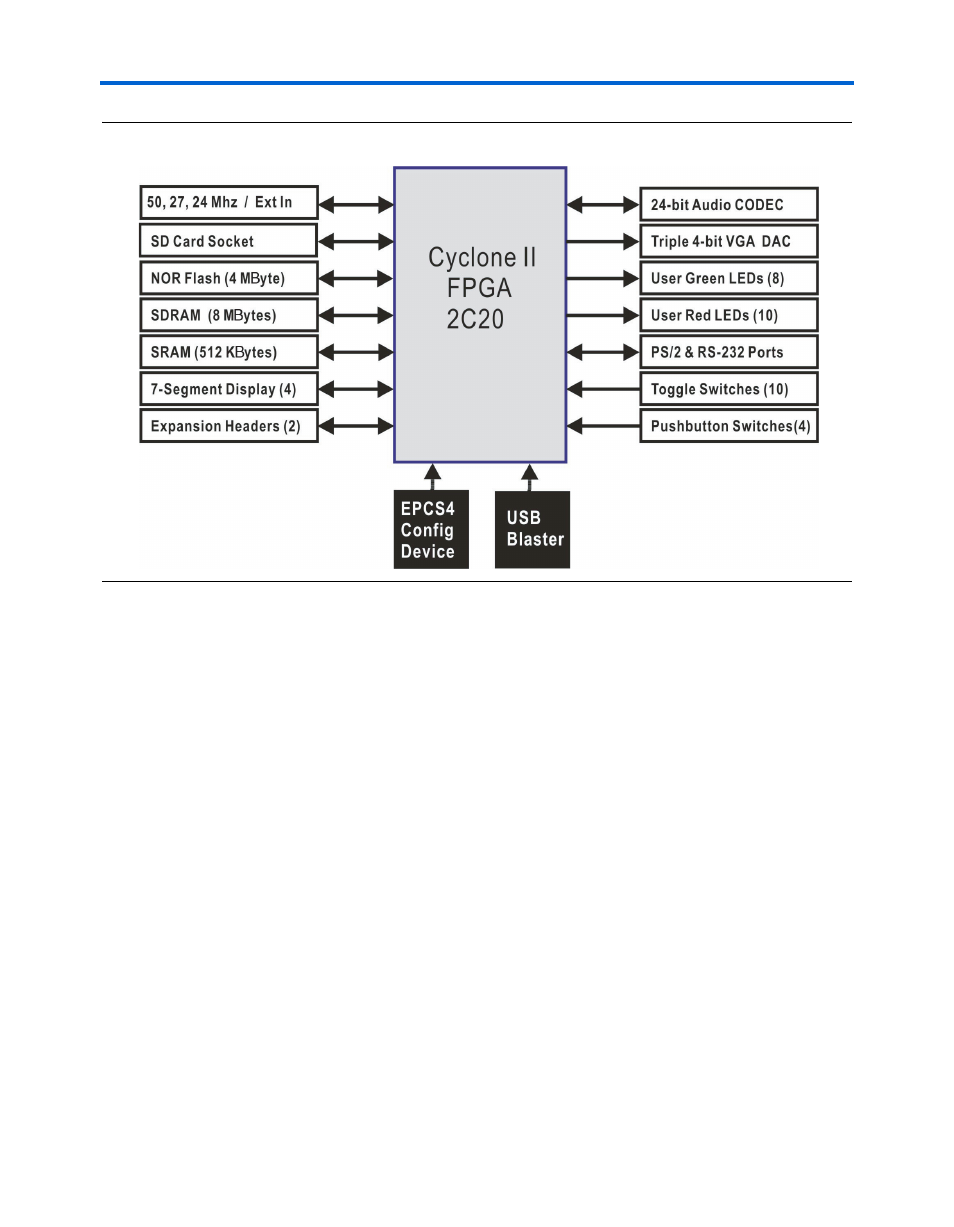

Figure 1–2. Development Board Block Diagram

Configuring the

Cyclone II FPGA

The Cyclone II FPGA Starter Development Board has integrated the

programming circuitry normally found in a USB-Blaster programming

cable, as well as a serial EEPROM chip (EPCS4) that stores configuration

data for the Cyclone II FPGA. This configuration data loads automatically

from the EEPROM chip into the FPGA each time power is applied to the

board.

Using the Quartus II software, it is possible to reprogram the FPGA at any

time, and it is also possible to change the non-volatile data stored in the

serial EEPROM chip. The following sections describe the two ways to

program the FPGA, JTAG programming and Active Serial (AS)

programming.

JTAG Programming

In this method of programming, named after the IEEE standards Joint Test

Action Group, the configuration bit stream downloads directly into the

Cyclone II FPGA through the USB-Blaster circuitry. The FPGA retains

this configuration as long as power is applied to the board; the FPGA

loses the configuration when the power is turned off.