Component features, Cyclone ii ep2c20 fpga, Component features –7 – Altera Cyclone II FPGA Starter Development Board User Manual

Page 15

Altera Corporation

Reference Manual

1–7

October 2006

Cyclone II FPGA Starter Development Board

Introduction

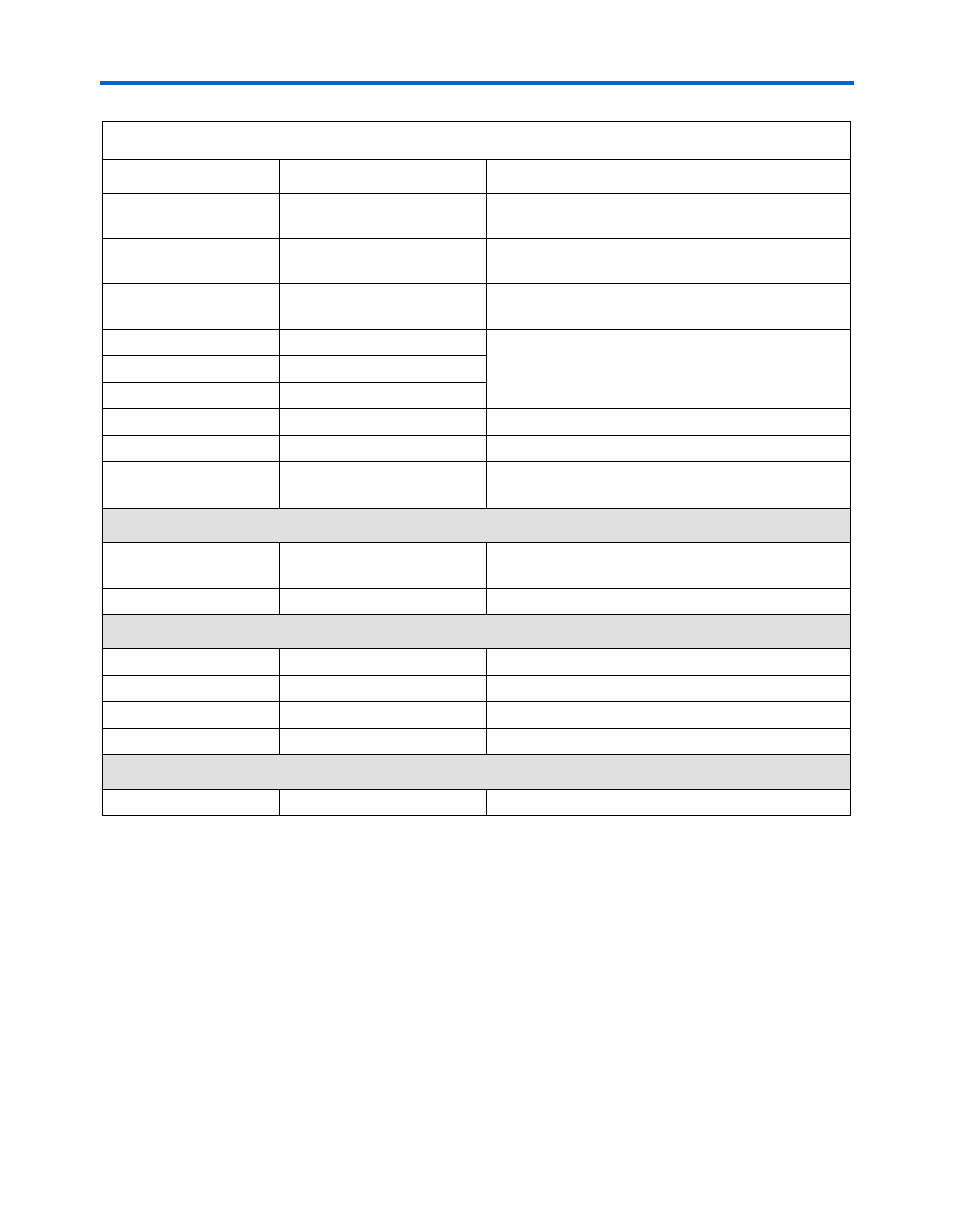

Component

Features

This section summarizes characteristics of each board component. For

detailed descriptions, refer to

.

Cyclone II EP2C20 FPGA

■

18,752 LEs

■

52 M4K RAM blocks

■

240K total RAM bits

■

26 embedded multipliers

■

4 PLLs

■

315 user I/O pins

RS232

Serial connector

RS-232 9-pin serial connector with 5 V-tolerant

buffers. Supports all RS-232 signals.

JP1

Expansion header connector Expansion header 1 connecting to 40 I/O pins on the

FPGA with resistor voltage protection

JP2

Expansion header connector Expansion header 2 connecting to 40 I/O pins on the

FPGA with resistor voltage protection

MIC

Microphone input

Audio CODEC connectors

LINEIN

Audio Line input

LINEOUT

Audio line output

VGA

VGA connector

VGA video port

SD CARD

SD card socket

Secure Data card socket

BLASTER

JTAG connector

USB Blaster Port JTAG connection to the MAX

®

configuration controller

Configuration & Reset

U16

Serial configuration device

Altera EPCS4 low-cost serial configuration device to

configure the FPGA

SW11

Power ON/OFF switch

Push-button switch to power up the board

Clock Circuitry

Y1

Oscillator

50 MHz clock signal driven to FPGA

Y2

Oscillator

27 MHz clock signal driven to FPGA

Y3

Oscillator

24 MHz clock signal driven to FPGA

EXT_CLOCK

External clock input

Connector to FPGA clock pin

Power Supply

DC7.5V

DC power jack

7.5 V DC unregulated power source

Table 1–1. Cyclone II FPGA Development Board Components & Interfaces (Part 2 of 2)

Board Designation

Name

Description