Flash schematic and pin list – Altera Cyclone II FPGA Starter Development Board User Manual

Page 29

Altera Corporation

Reference Manual

2–11

October 2006

Cyclone II FPGA Starter Development Board

Development Board Components

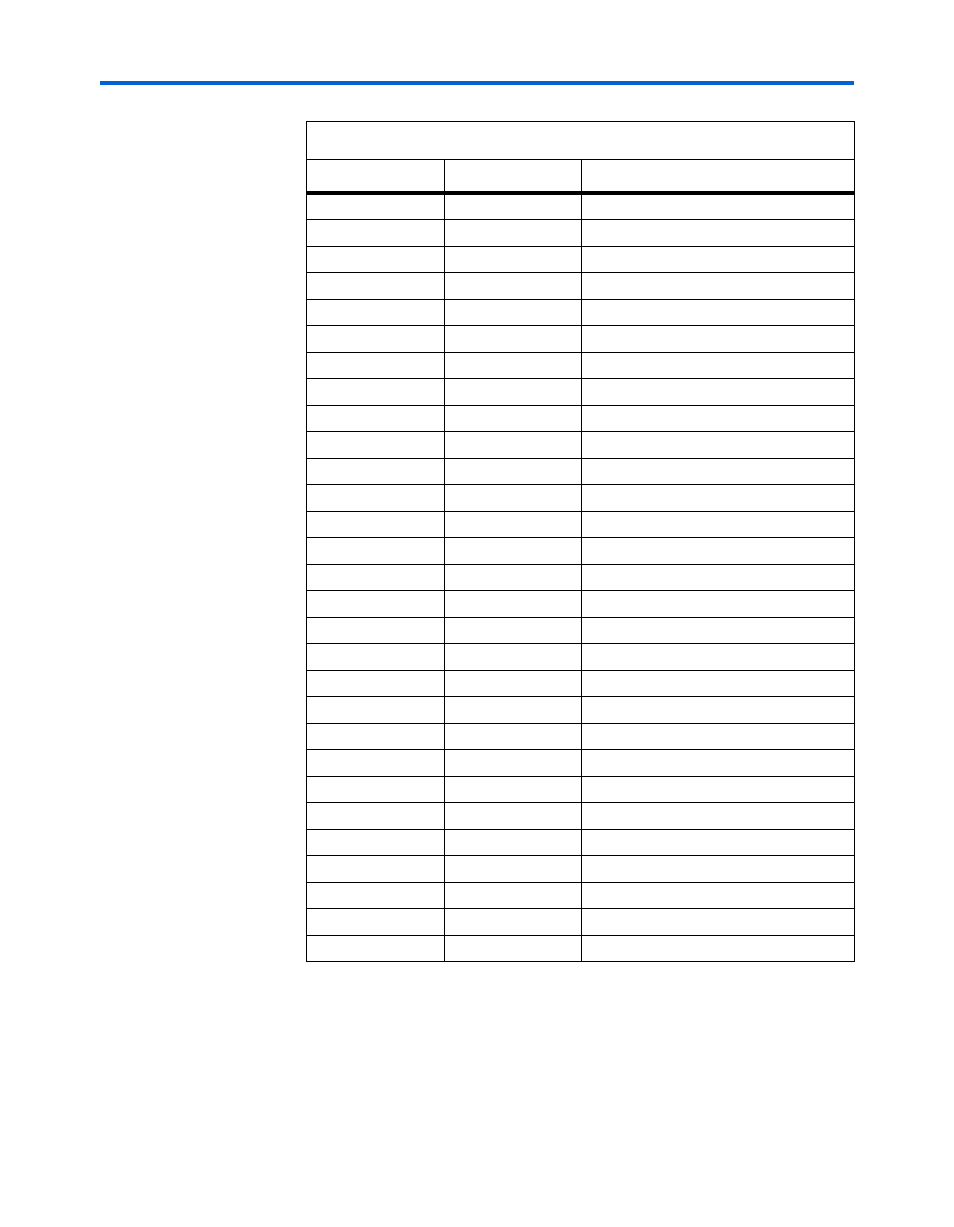

Flash Schematic and Pin List

shows the Flash memory interface signals.

SRAM_ADDR[10]

PIN_R11

SRAM Address[10]

SRAM_ADDR[11]

PIN_T11

SRAM Address[11]

SRAM_ADDR[12]

PIN_Y10

SRAM Address[12]

SRAM_ADDR[13]

PIN_U10

SRAM Address[13]

SRAM_ADDR[14]

PIN_R10

SRAM Address[14]

SRAM_ADDR[15]

PIN_T7

SRAM Address[15]

SRAM_ADDR[16]

PIN_Y6

SRAM Address[16]

SRAM_ADDR[17]

PIN_Y5

SRAM Address[17]

SRAM_DQ[0]

PIN_AA6

SRAM Data[0]

SRAM_DQ[1]

PIN_AB6

SRAM Data[1]

SRAM_DQ[2]

PIN_AA7

SRAM Data[2]

SRAM_DQ[3]

PIN_AB7

SRAM Data[3]

SRAM_DQ[4]

PIN_AA8

SRAM Data[4]

SRAM_DQ[5]

PIN_AB8

SRAM Data[5]

SRAM_DQ[6]

PIN_AA9

SRAM Data[6]

SRAM_DQ[7]

PIN_AB9

SRAM Data[7]

SRAM_DQ[8]

PIN_Y9

SRAM Data[8]

SRAM_DQ[9]

PIN_W9

SRAM Data[9]

SRAM_DQ[10]

PIN_V9

SRAM Data[10]

SRAM_DQ[11]

PIN_U9

SRAM Data[11]

SRAM_DQ[12]

PIN_R9

SRAM Data[12]

SRAM_DQ[13]

PIN_W8

SRAM Data[13]

SRAM_DQ[14]

PIN_V8

SRAM Data[14]

SRAM_DQ[15]

PIN_U8

SRAM Data[15]

SRAM_WE_N

PIN_AA10

SRAM Write Enable

SRAM_OE_N

PIN_T8

SRAM Output Enable

SRAM_UB_N

PIN_W7

SRAM High-byte Data Mask

SRAM_LB_N

PIN_Y7

SRAM Low-byte Data Mask

SRAM_CE_N

PIN_AB5

SRAM Chip Enable

Table 2–7. SRAM FPGA Pin Connections (Part 2 of 2)

Signal Name

FPGA Pin

Description