Usb-blaster controller, Epcs4, Vga dac – Altera Cyclone II FPGA Starter Development Board User Manual

Page 20: Usb-blaster controller –2 epcs4 –2 vga dac –2

2–2

Reference Manual

Altera Corporation

Cyclone II FPGA Starter Development Board

October 2006

Development Board Components

f

For Cyclone II-related documentation including pin out data for the

EP2C20 device, refer to the Altera Cyclone II literature page at

www.altera.com/literature/lit-cyc2.jsp

.

USB-Blaster

Controller

The Cyclone II FPGA Starter Development Board includes an integrated

USB-Blaster controller. Accessed across a USB-Blaster cable connection by

Altera USB-Blaster driver software on a host computer, the USB-Blaster

controller enables direct programming of the FPGA.

f

Refer to ((section on Configuring the FPGA)) and the Cyclone II FPGA

Starter Development Kit User Guide for further details on configuring the

FPGA.

EPCS4

The Cyclone II FPGA Starter Development Board includes a serial EPCS4

EEPROM chip that stores configuration data for the Cyclone II FPGA. The

EPCS4 device automatically loads stored configuration data into the

FPGA each time power is applied to the board.

Quartus II software on a host computer connected to the board across a

USB-Blaster cable and controller can change the non-volatile data stored

in the serial EEPROM chip. The EPCS4 device can store FPGA

configuration data, or program data, or both.

f

“Configuring the Cyclone II FPGA” on page 1–3

and the Cyclone

II FPGA Starter Development Kit User Guide for further details on

configuring the FPGA. Refer to the Serial Configuration Devices chapter in

the Altera Configuration Device Handbook for more information about the

EPCS4 device.

VGA DAC

The development board includes a 4-bit VGA digital-to-analog converter

(DAC) that can produce standard VGA output with a resolution of

640x480 pixels at 25 MHz. With the VGA DAC able to support a refresh

rate up to 100 MHz, a user can implement a high-performance TV

Encoder on the FPGA.

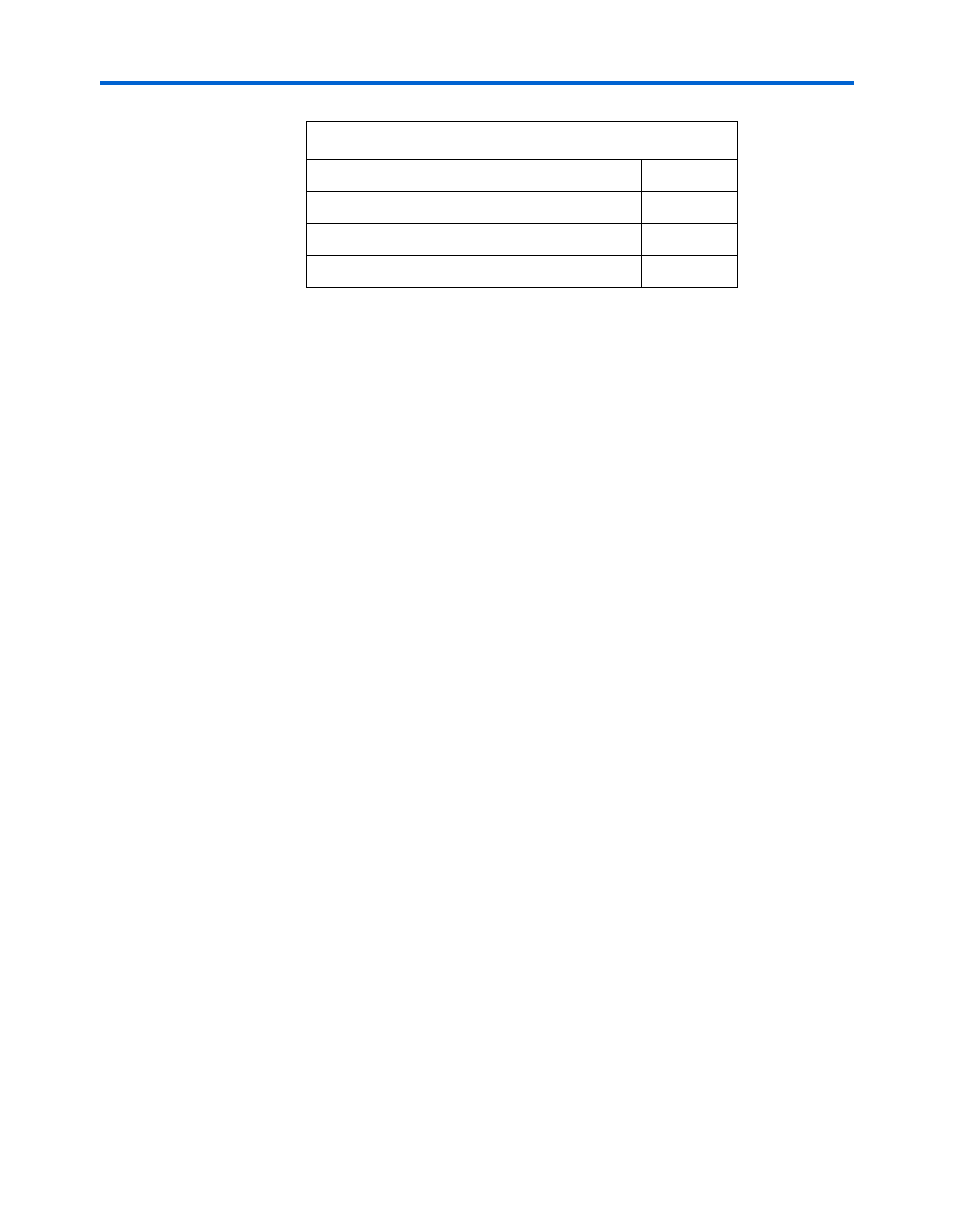

Total RAM Bits

240K

Embedded 18x18 Multiplier Blocks

26

PLLs

4

User I/O Pins

315

Table 2–1. Cyclone II EP2C20 FPGA Features (Part 2 of 2)