Table 8-10, Spp and other status signals, Table 8-11 – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 251: Scratch register, Cpld and fpga, 4 scratch register

Advertising

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

251

8.1.2.2.4 Scratch Register

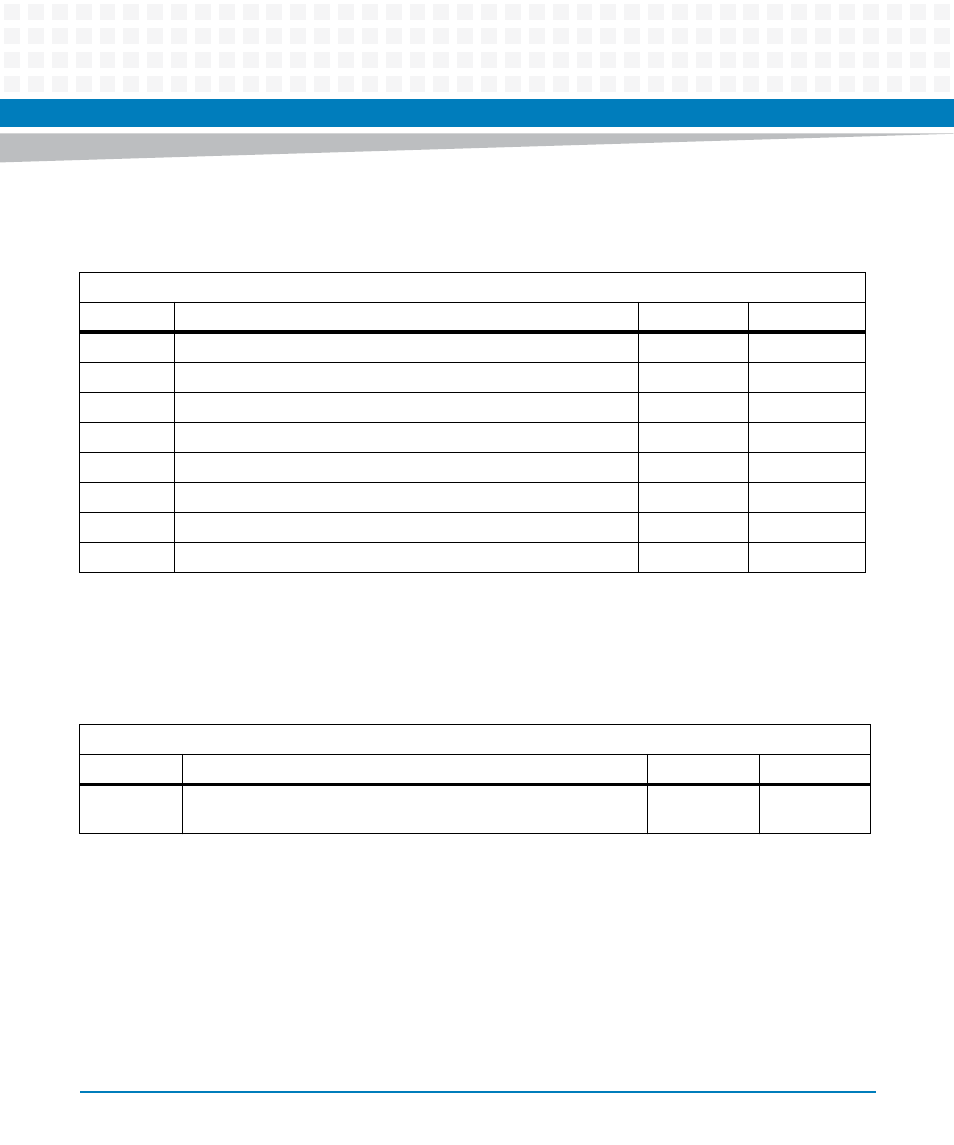

Table 8-10 SPP and other Status Signals

CPLD Address: 0x06

Bit

Description

Default

Access

0

SPP P4080 ASLEEP. Level of SPP_ASLEEP Signal.

ext.

r

1

SPP Temp sensor alert. Level of SPP_TEMP_ALERT_ Signal.

ext.

r

2

ATCA Power Brick Alarm. Level of APB_ALARM Signal.

ext.

r

3

RTM PS1 from Zone 3 P30 present. Level of RTM_PS1_Signal.

ext.

r

4

Level of IPMC Signal IPMC_COM2FP.

ext.

r

5

Level of IPMC spare signal IPMC_SPARE]

ext.

r

6

Level of IPMC spare signals WDOG_EXPIRED_RESET_

ext.

r

7:5

Reserved

0

r

Table 8-11 Scratch Register

Address: 0x07

Bit

Description

Default

Access

7:0

Scratch Register.

0

SPI: r/w

SPP: r

Advertising

This manual is related to the following products: