Table 8-128, Gpp scratch register, Table 8-129 – Artesyn ATCA-8310 Installation and Use (May 2014) User Manual

Page 327: Ipmc scratch register, Table 8-130, Spp and ipmc access to gpp port 80, Cpld and fpga

Advertising

CPLD and FPGA

ATCA-8310 Installation and Use (6806800M72E)

327

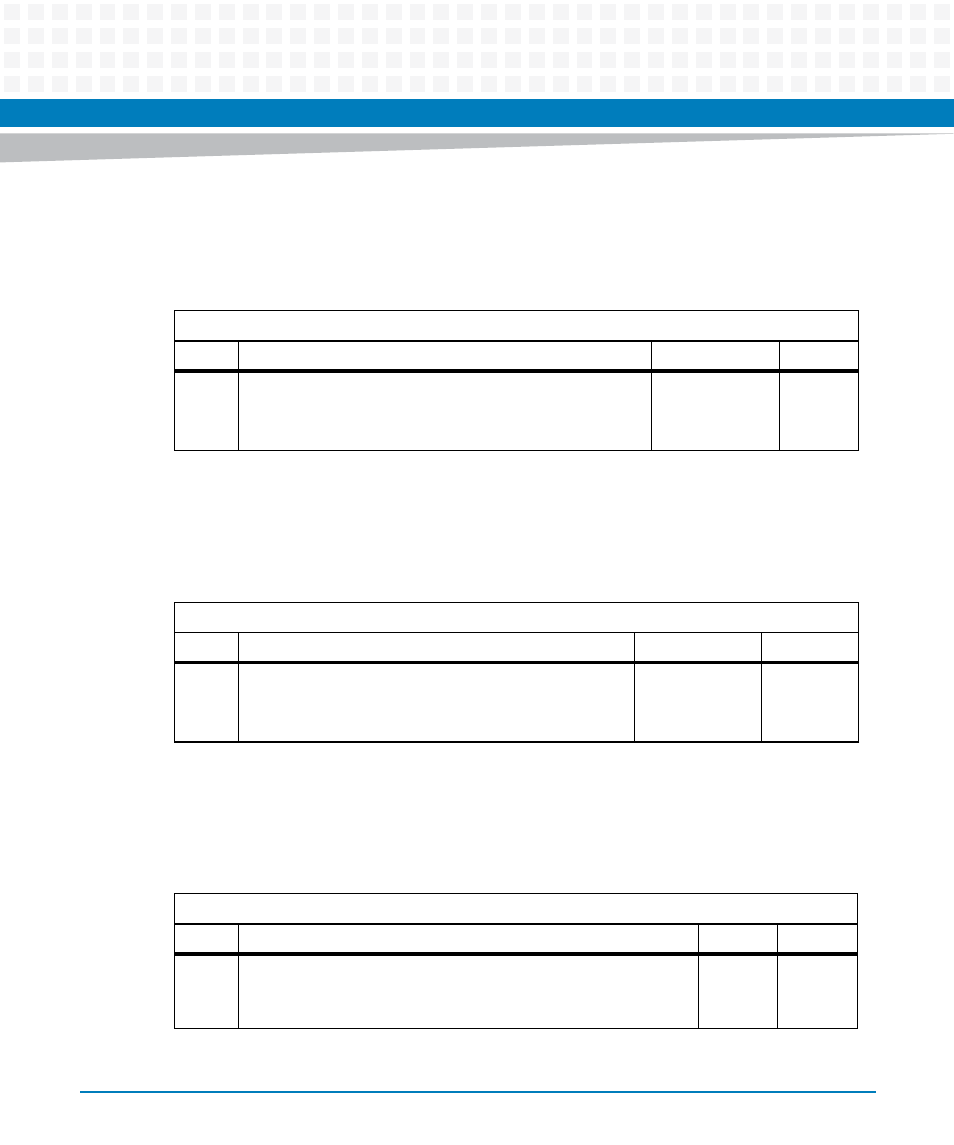

8.2.2.3.31 GPP Scratch Register

8.2.2.3.32 IPMC Scratch Register

8.2.2.3.33 SPP and IPMC access to GPP Port 80

Table 8-128 GPP Scratch Register

Address: 0x7D

Bit Description

Default

Access

7:0

SPP Scratch Register.

PWR_GOOD:0

GPP: r/w

SPP: r

IPMC: r

Table 8-129 IPMC Scratch Register

Address: 0x7E

Bit Description

Default

Access

7:0

IPMC Scratch Register.

PWR_GOOD:0

IPMC: r/w

SPP: r

GPP: r

Table 8-130 SPP and IPMC access to GPP Port 80

Address: 0x7F

Bit Description

Default

Access

7:0

GPP Port 0x80.

Note: GPP has access to Port 0x80 Register via dedicated GPP LPC

IO address 0x080

0

IPMC: r

SPP: r

Advertising

This manual is related to the following products: