Altera PowerPlay Early Power Estimator User Manual

Page 24

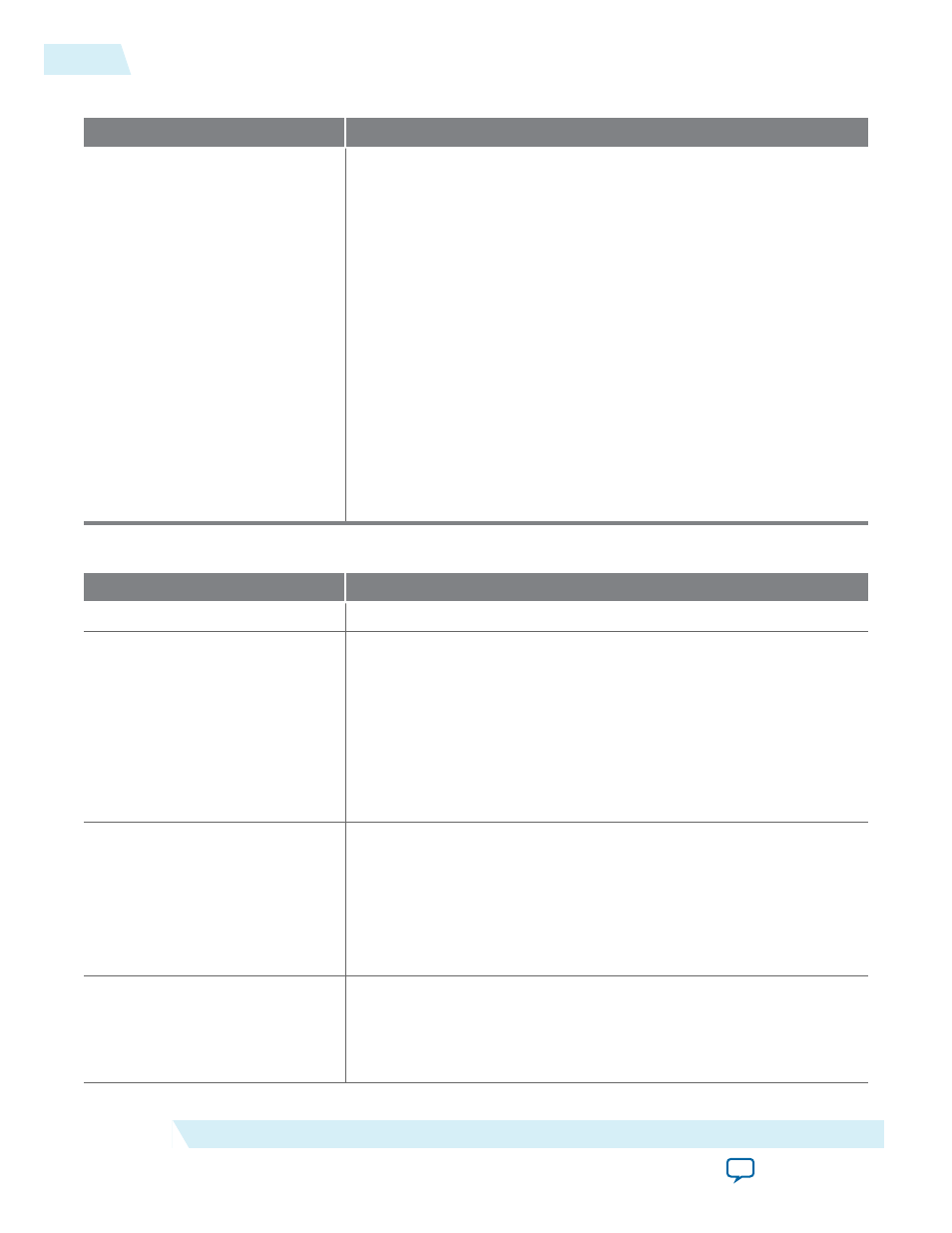

Table 3-4: General Settings in the Logic Worksheet

Input Parameter

Description

High-Speed Tile Usage

Select the High-Speed Tile Usage setting. This value can be Typical

Design, Typical High-Performance Design, or Atypical High-

Performance Design.

• Typical Design represents a design with 10% or more timing

margin.

• Typical High-Performance Design represents an average design

with no timing margin. These designs have a few near-critical

timing paths.

• Atypical High-Performance Design represents a 90

th

percentile

design with no timing margin. These designs have many near-

critical timing paths.

This primarily impacts static power consumption (P

STATIC

) found in

the Main worksheet of the PowerPlay EPE spreadsheet. It also has a

small impact on the dynamic power consumed by the logic resources

entered in the Logic worksheet of the PowerPlay EPE spreadsheet.

This option is only available for Arria V GZ, Stratix III, Stratix IV, and

Stratix V devices.

Table 3-5: Logic Worksheet Information

Column Heading

Description

Module

Specify a name for each module of the design. This is an optional entry.

#Combinational ALUTs/#LUTs Enter the number of combinational ALUTs or look-up tables (LUTs).

This is the “Combinational ALUTs” value from the Quartus II

Compilation Report Resource Usage Summary section.

For Arria II, Arria V GZ, Stratix III, Stratix IV, and Stratix V devices,

each adaptive logic module (ALM) contains up to two combinational

ALUTs. Smaller ALUTs consume less power than larger ALUTs, but

the device can fit more of them. The total number of ALUTs in the

design must not exceed (the number of ALMs) × two.

#FFs

Enter the number of flipflops in the module.

This is the sum of “Register ALUTs” and “Dedicated logic registers”

from the Quartus II Compilation Report Resource Usage Summary

section.

Clock routing power is calculated separately on the Clock worksheet of

the PowerPlay EPE spreadsheet.

Clock Freq (MHz)

Enter a clock frequency (in MHz). This value is limited by the

maximum frequency specification for the device family.

100 MHz with a 12.5% toggle means that each LUT or flipflop output

toggles 12.5 million times per second (100 × 12.5%).

3-14

Logic Worksheet

UG-01070

2015.01.20

Altera Corporation

PowerPlay Early Power Estimator Worksheets