Altera Arria II GX FPGA Development Board User Manual

Page 24

2–16

Chapter 2: Board Components

Configuration, Status, and Setup Elements

Arria II GX FPGA Development Board Reference Manual

February 2011

Altera Corporation

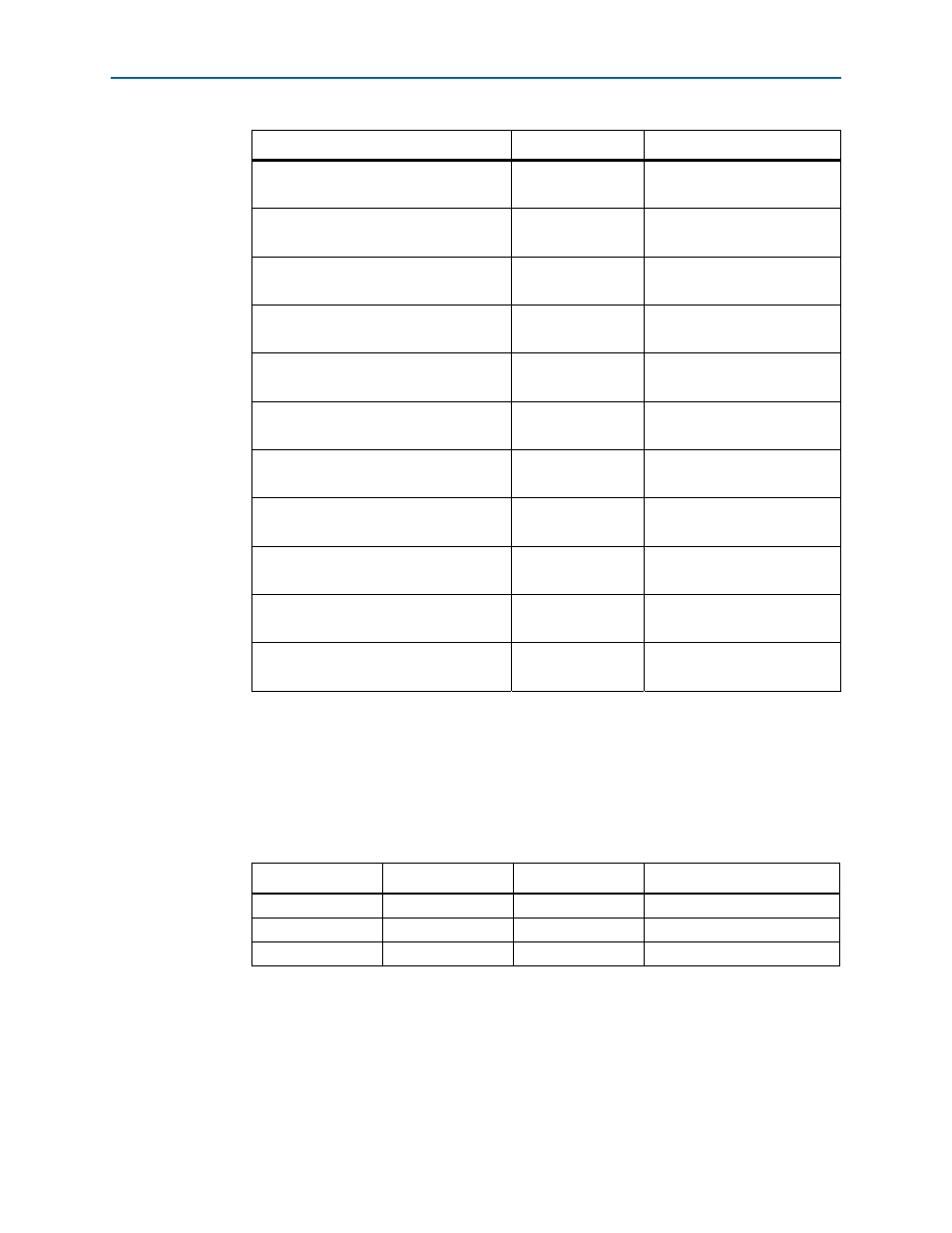

There are two pages reserved for the user FPGA configuration data. The factory

hardware page (page 0) loads upon power-up if the USER LOAD DIP switch (SW4.4) is

set to '1'. Otherwise, the user hardware page (page 1) is loaded. Pressing the load

image push-button switch (PB5) loads the FPGA with a hardware page based on

which CONFIG_LED[2:0] (D11, D12, D13) illuminates.

defines the hardware

page that loads when you press the load image push-button switch (PB5).

User software

24,320

0x03FD-FFFF

0x0282-0000

Factory software

8,192

0x0281-FFFF

0x0202-0000

zipfs — HTML, web content

8,192

0x0201-FFFF

0x0182-0000

Unused

6,095

0x0181-FFFF

0x0128-0000

User hardware 2

6,357

0x0127-FFFF

0x00C6-0000

User hardware 1

6,357

0x00C5-FFFF

0x0064-0000

Factory hardware

6,357

0x0063-FFFF

0x0002-0000

PFL option bits

32

0x0001-FFFF

0x0001-8000

Board information

32

0x0001-7FFF

0x0001-0000

Ethernet option bits (MAC address)

32

0x0000-FFFF

0x0000-8000

User design reset vector

32

0x0000-7FFF

0x0000-0000

Table 2–10. Load Image Push-Button Switch (PB5) LED Settings

IMAGE0

IMAGE1

IMAGE2

Design

ON

OFF

OFF

Factory hardware

OFF

ON

OFF

User hardware 1

OFF

OFF

ON

User hardware 2

Notes to

(1) ON indicates a setting of ’1’.

(2) OFF indicates a setting of ’0’.

Table 2–9. Flash Memory Map (Part 2 of 2)

Name

Size (KB)

Address