Pci operating mode, speed & dip switch settings, Memory, Ddr2 sdram memory – Altera Cyclone II EP2C35 PCI Development Board User Manual

Page 15: Epcs64 serial configuration (flash) devices

Altera Corporation

Core Version 4.0.0

2–5

May 2005

Cyclone II EP2C35 PCI Development Board Reference Manual

Board Components & Interfaces

PCI Operating Mode, Speed & DIP Switch Settings

, and

list the board’s PCI operating mode and speed,

and the corresponding DIP switch (S4) bank setting.

Memory

The board has the following memory components:

■

Two 32-MByte DDR2 SDRAM devices

■

Two EPCS64 serial configuration (flash) devices

DDR2 SDRAM Memory

The board was tested with the Altera 167-MHz, DDR2 SDRAM Controller

MegaCore function version 3.2.0. Two 16M × 16 DDR2 SDRAM devices

are connected to banks 3 and 4 of the Cyclone II device as a single

16M × 32 memory block.

EPCS64 Serial Configuration (Flash) Devices

The board has two EPCS64Sl16N serial configuration devices (U7 and

U19) that upon power-up programs the Cyclone II device. The board

contains one EPCS64Sl16N device that is user-programmable, and one

preloaded, factory-programmed EPCS64Sl16N device.

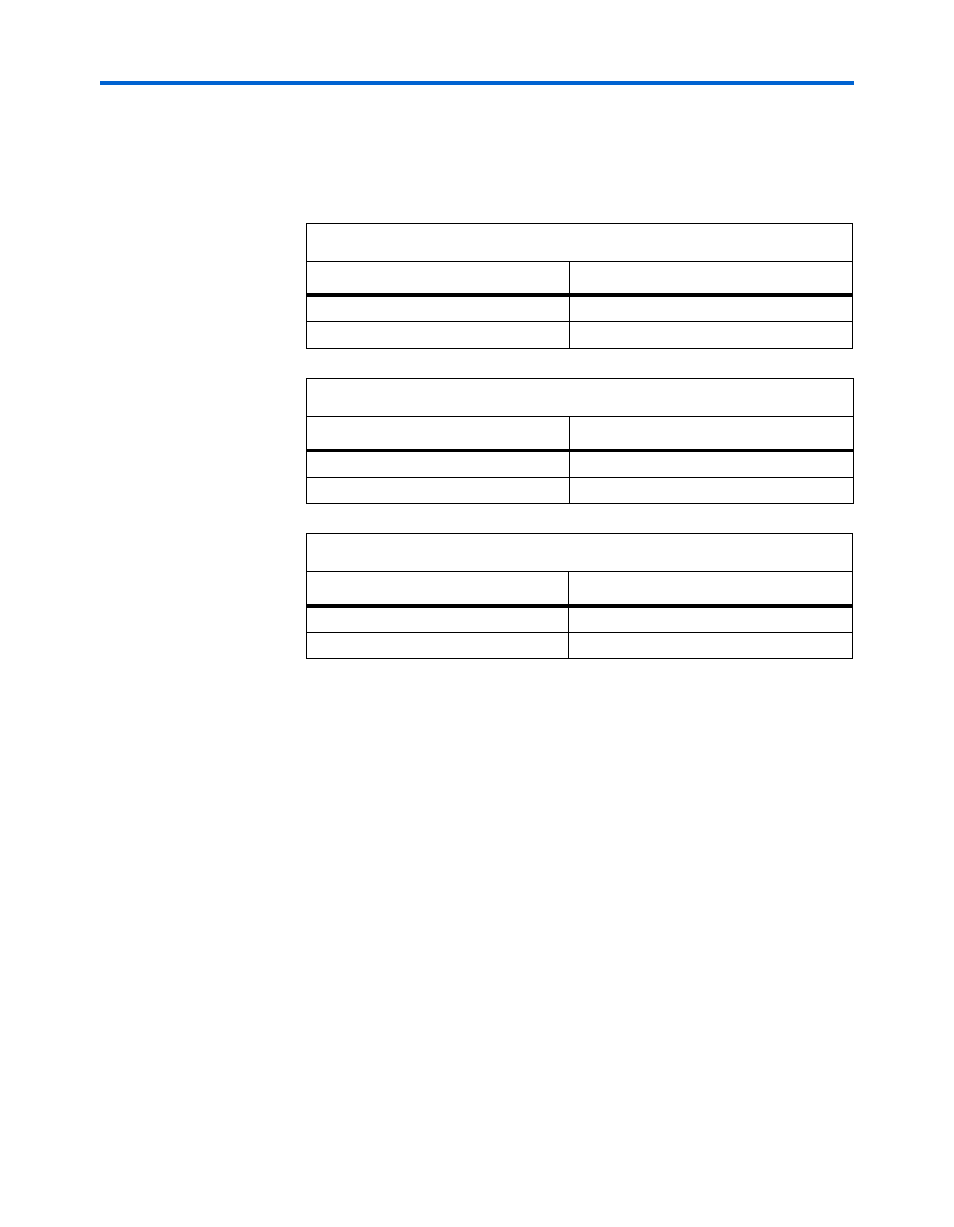

Table 2–3. PCI Operating Mode Setting

DIP Switch Position 1 (PCI Mode)

PCI Operating Mode

Off

PCI-X at the speed shown in

On

PCI at the speed shown in

Table 2–4. PCI Operating Speed Setting

DIP Switch Position 3 (PCI SPD)

PCI Operating Speed (MHz)

Off

66 MHz

On

33 MHz

Table 2–5. PCI-X Operating Speed Setting

DIP Switch Position 2 (PCI XSPD)

PCI-X Operating Speed (MHz)

Off

133 or 100 MHz

On

66 MHz