Altera Cyclone II EP2C35 PCI Development Board User Manual

Page 40

4–6

Core Version 4.0.0

Altera Corporation

Cyclone II EP2C35 PCI Development Board Reference Manual

May 2005

Memory

DDR2_A1

M3

M3

N/A

RN13.6

A20

DDR2_A2

M7

M7

N/A

RN11.4

A21

DDR2_A3

N2

N2

N/A

RN13.8

B19

DDR2_A4

N8

N8

N/A

RN11.1

B21

DDR2_A5

N3

N3

N/A

RN11.7

B22

DDR2_A6

N7

N7

N/A

RN13.1

C19

DDR2_A7

P2

P2

N/A

RN13.7

D18

DDR2_A8

P8

P8

N/A

R25

D19

DDR2_A9

P3

P3

N/A

RN13.5

D20

DDR2_A10

M2

M2

N/A

RN9.3

A4

DDR2_A11

P7

P7

N/A

RN9.5

A5

DDR2_A12

R2

R2

N/A

RN9.7

B4

DDR2_A13

R8

R8

N/A

RN9.6

B5

DDR2_A14

R3

R3

N/A

RN9.8

B6

DDR2_A15

R7

R7

N/A

RN9.4

C4

DDR2_BA0

L2

L2

N/A

RN11.8

C22

DDR2_BA1

L3

L3

N/A

RN11.5

C21

DDR2_BA2

L1

L1

N/A

R21

C11

DDR2_DQS0

-

F7

RN14.3

RN17.1

C17

DDR2_DQS1

-

B7

RN10.8

RN16.5

B14

DDR2_DQS2

F7

-

RN7.8

RN3.4

B8

DDR2_DQS3

B7

-

RN6.7

RN2.4

C12

DDR2_DM0

-

F3

RN14.5

RN17.3

C16

DDR2_DM1

-

B3

RN12.6

RN16.4

G12

DDR2_DM2

F3

-

RN7.3

RN3.7

D6

DDR2_DM3

B3

-

RN6.2

RN2.3

B9

DDR2_DQ0

-

G8

RN14.4

RN15.8

A18

DDR2_DQ1

-

G2

RN14.8

RN17.6

G16

DDR2_DQ2

-

H7

RN14.6

RN15.7

F16

DDR2_DQ3

-

H3

RN12.8

RN17.2

F15

DDR2_DQ4

-

H1

RN14.7

RN17.5

G15

DDR2_DQ5

-

H9

RN14.1

RN15.5

B17

DDR2_DQ6

-

F1

RN14.2

RN17.4

A17

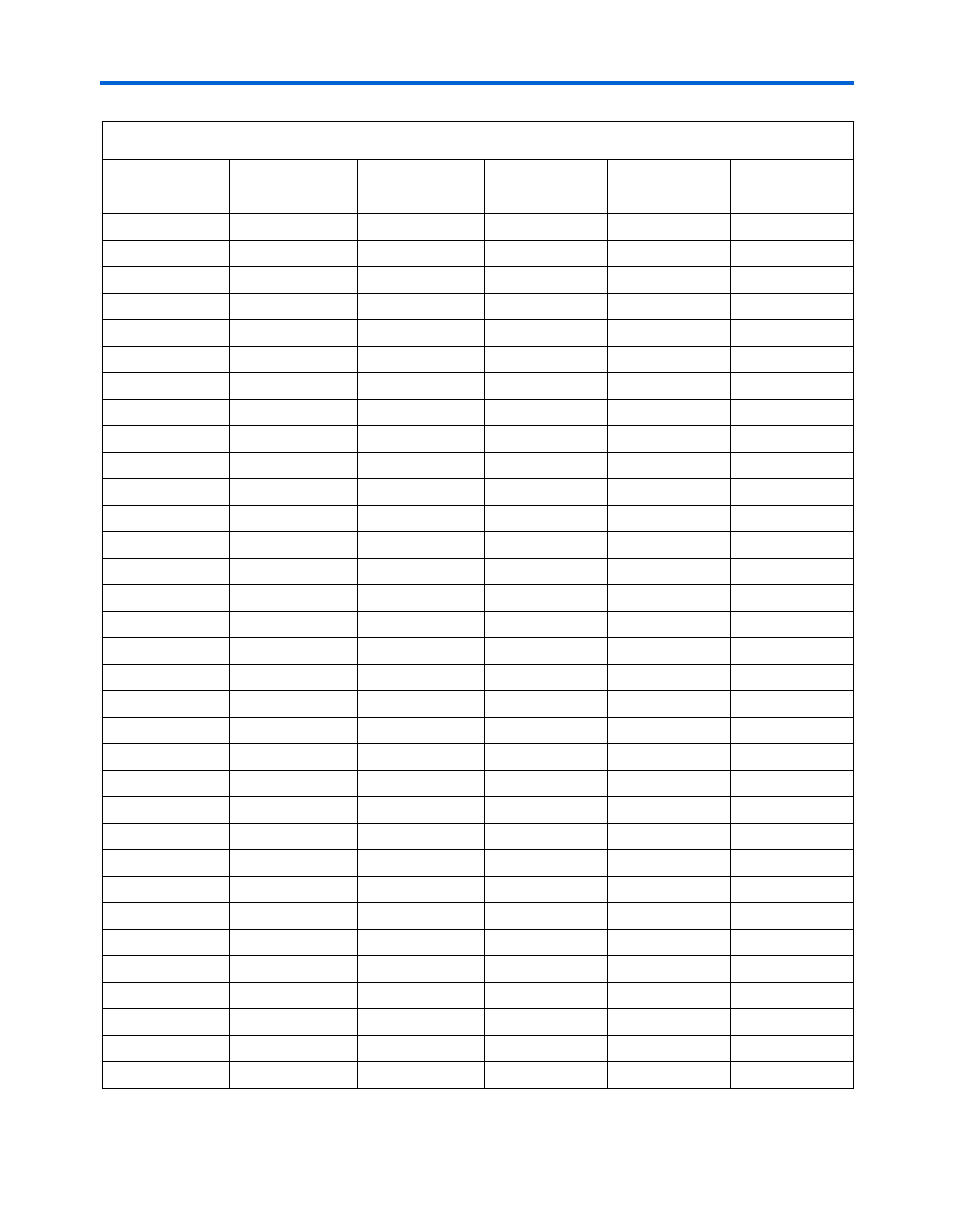

Table 4–3. DDR2 SDRAM Memory & Terminator Signal Connections (Part 2 of 3)

DDR2 SDRAM

Signal

DDR2 SDRAM

Device 1 (U6)

DDR2 SDRAM

Device 2 (U10)

Non Fly-By

Terminator

Fly-By

Terminator

Cyclone II Pin

(U9)