Clocks & clock distribution, Sma clock input requirements – Altera Cyclone II EP2C35 PCI Development Board User Manual

Page 16

2–6

Core Version 4.0.0

Altera Corporation

Cyclone II EP2C35 PCI Development Board Reference Manual

May 2005

Component Operation

f

For more information on serial configuration devices, refer to the Serial

Configuration Devices (EPCS1, EPCS4, EPCS16 & EPCS64) Data Sheet

chapter in volume 2 of the Configuration Handbook.

Clocks & Clock Distribution

The board has two clock sources driven directly to the Cyclone II device.

Using the PLLs integrated within the Cyclone II device, the designer has

significant flexibility to achieve the appropriate clock configuration.

Table 2–6

shows the board’s clock sources.

f

Refer to the PLLs in Cyclone II Devices chapter in the Cyclone II Device

Handbook for more information.

SMA Clock Input Requirements

The SMA clock input, CLK_SMA, can be provided by an external signal

source through the J5 connector. Use a 50-

Ω signal source and cable with

an LVTTL-type signal (square-wave, with a voltage swing from 0.0 to

+3.3 V). The maximum CLK_SMA input frequency is 464 MHz; the

maximum board frequency with the SMA clock is 500 MHz.

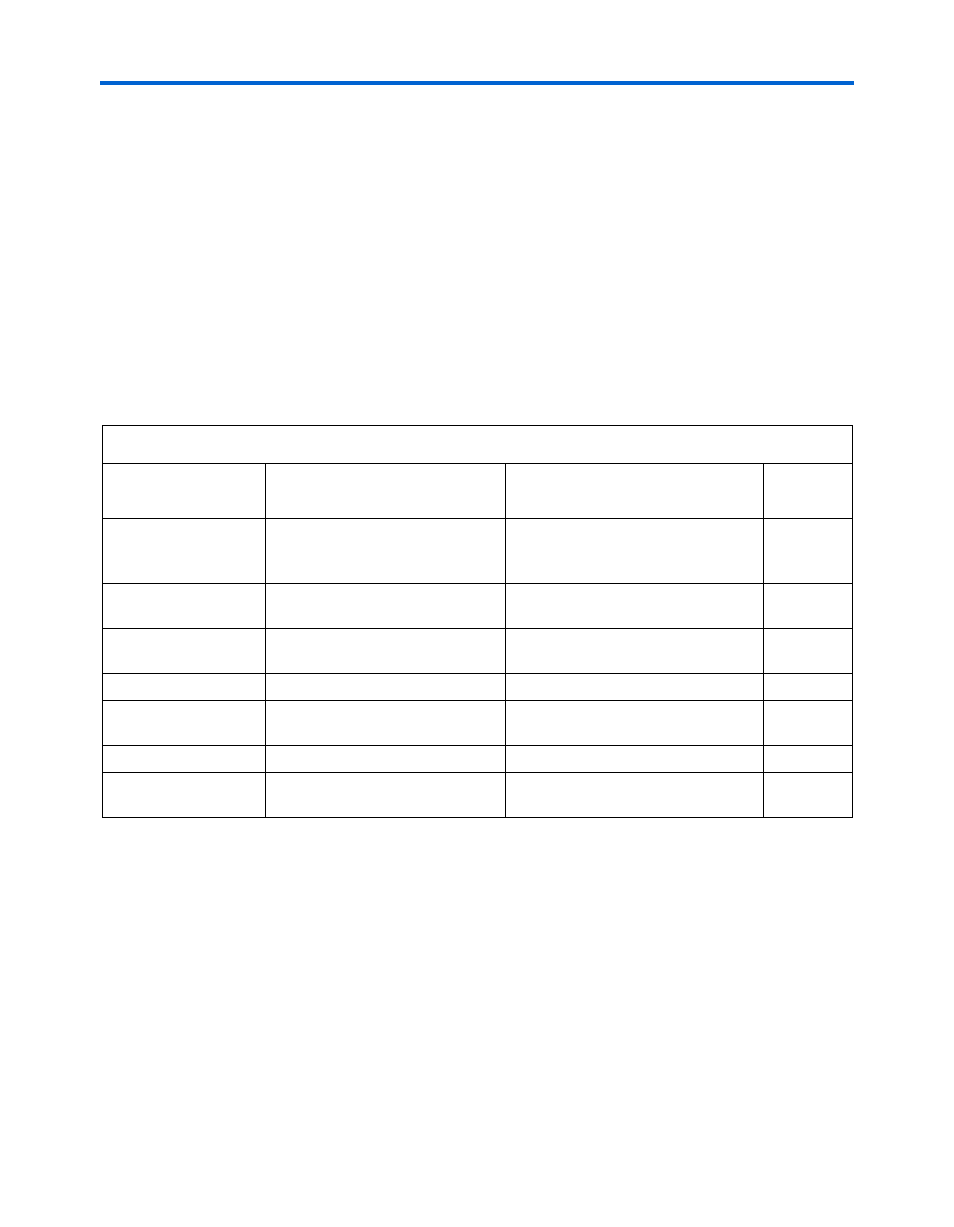

Table 2–6. Cyclone II EP2C35 PCI Development Board Clock Sources

Signal Name

Source

Destination

Primary

PLL

(1)

LPCIX_CLK

PCI connector (J13.B16) through

level shifter (U13.13 and U13.11)

and resistor (R29)

Cyclone II device (U9.P26)

PLL2

OSCA_CLK1

Socketed 100-MHz oscillator

(J4.5) through resistor (R61)

Cyclone II device (U9.N1)

PLL1

OSCA_CLK6

Socketed 100-MHz oscillator

(J4.5) through resistor (R62)

Cyclone II device (U9.P25)

PLL2

CLK_SMA

SMA clock input connector (J5.1)

Cyclone II device (U9.N2)

PLL1

CLK_FROM_PROTO1

Altera daughter card (PROTO1)

(J7.13)

Cyclone II device (U9.P2)

PLL1

DDR2_SYNC_CLK

Cyclone II device (U9.B7)

Cyclone II device (U9.AF14)

PLL4

CLK_25MHZ

On-board 25-MHz 10/100

Ethernet oscillator (OSC1.4)

Ethernet MAC/PHY device (U3.127)

N/A

Note:

(1)

A global clock input can directly feed Cyclone II PLLs.

Table 2–6

shows the direct connections and does not show

the connection via global clock networks.