Altera Stratix II GX EP2SGX90 Transceiver Signal Integrity Development Board User Manual

Page 23

Altera Corporation

Reference Manual

2–13

May 2006

Stratix II GX EP2SGX90 Transceiver Signal Integrity Development Board

Board Components & Interfaces

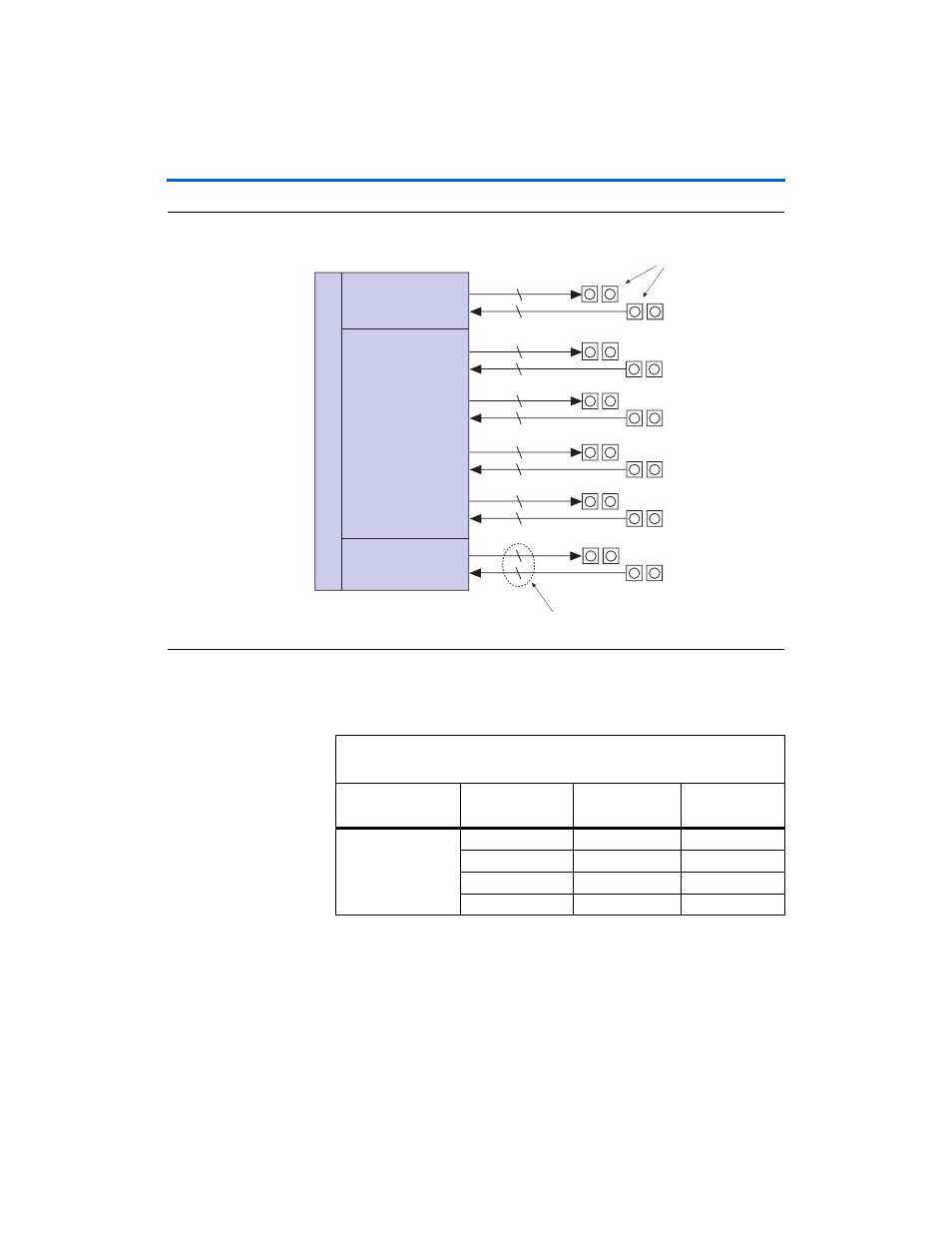

Figure 2–6. SMA Connector Block Diagram

lists transceiver block’s transmit and receive signals,

corresponding SMA reference designators and FPGA pins.

Transcei

v

er Block 1

1 Channel

Transcei

v

er Block 2

4 Channels

Transcei

v

er Block 3

1 Channel

Stratix II GX Device

Transceiver Block

TX: 40 inch trace length

SMA Connectors

(J27, J2

8

)

(J29, J26)

(J43, J45)

(J42, J44)

(J39, J40)

(J3

8

, J41)

(J32, 33)

(J30, J31)

(J36, J37)

(J34, 35)

(J47, J4

8

)

(J49, J46)

Table 2–8. Transceiver Block Corresponding Signals, SMA Designator, and

FPGA Pin (Part 1 of 2)

Block

Signal

SMA Reference

Designator

Stratix II GX Pin

Transceiver Block 1,

1 Channel

TX_P0

J27

A4

TX_N0

J28

A5

RX_P0

J29

C1

RX_N0

J26

C2