Push-button switches (s1 through s6), Push-button switches (s1 through s6) -21 – Altera Stratix II GX EP2SGX90 Transceiver Signal Integrity Development Board User Manual

Page 31

Altera Corporation

Reference Manual

2–21

May 2006

Stratix II GX EP2SGX90 Transceiver Signal Integrity Development Board

Board Components & Interfaces

Push-Button Switches (S1 Through S6)

Board references S1 through S6 are push-button switches allowing

general user I/O interfaces to the Stratix II GX device.

S1-S6 are user-defined, momentary-contact push-button switches used to

provide stimulus to a user design on the board. Each push-button is

connected through debounce circuitry to a Stratix II GX general-purpose

I/O pin as listed in

. When the switch is pressed and held

down, the device pin is set to logic 0, when the switch is released, the

device pin is set to logic 1.

The push button device is a small form factor switch similar to the

Panasonic Tactile Switches (EVQPAC07K).

provides

operational descriptions and schematic signal names.

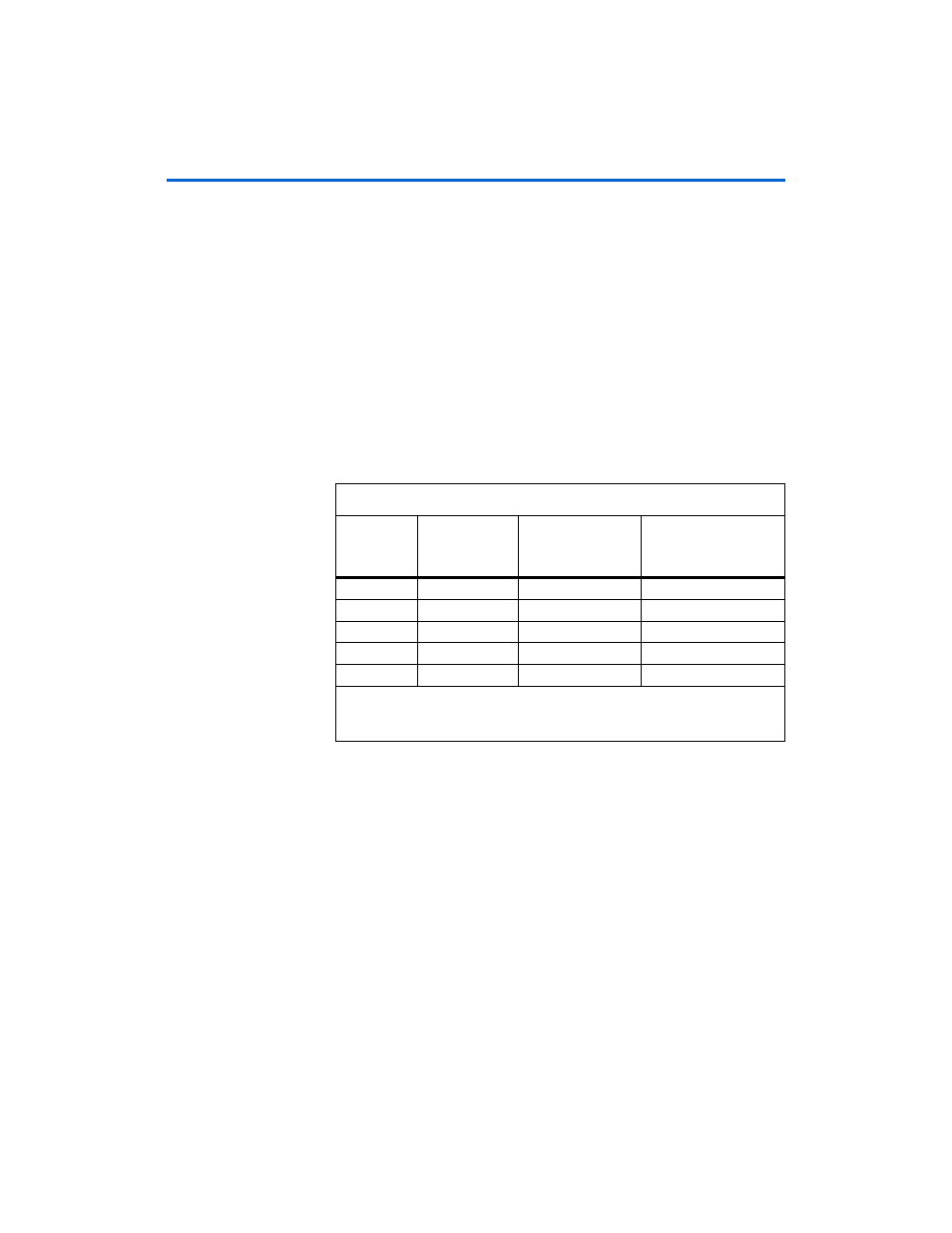

Table 2–13. Push-Button Switches (S1 Through S6)

Push-Button

Name

Board

Reference

Designator

Schematic Signal

Name

Stratix II GX Device

(U20) Pin Number

PB0

S1

PB0_IN

AD28

PB1

S2

PB1_IN

AF34

PB2

S3

PB2_IN

AF33

PB3

S4

PB3_IN

AF30

PB4

S5

PB4_IN

AF29

Note to

:

(1)

The PB5 is a special purpose button, called DEV_CLRn, connected to the AH20 pin

of the FPGA. The PB5 clears the FPGA data.