Altera Stratix II GX EP2SGX90 Transceiver Signal Integrity Development Board User Manual

Page 25

Altera Corporation

Reference Manual

2–15

May 2006

Stratix II GX EP2SGX90 Transceiver Signal Integrity Development Board

Board Components & Interfaces

Also, the 1 M Baud rate should be sufficient for the intended

communication applications. The FTDI circuit also has a downloadable

non-license USB direct driver and SLL software interface that configures

the USB connection into the host PC’s COM port.

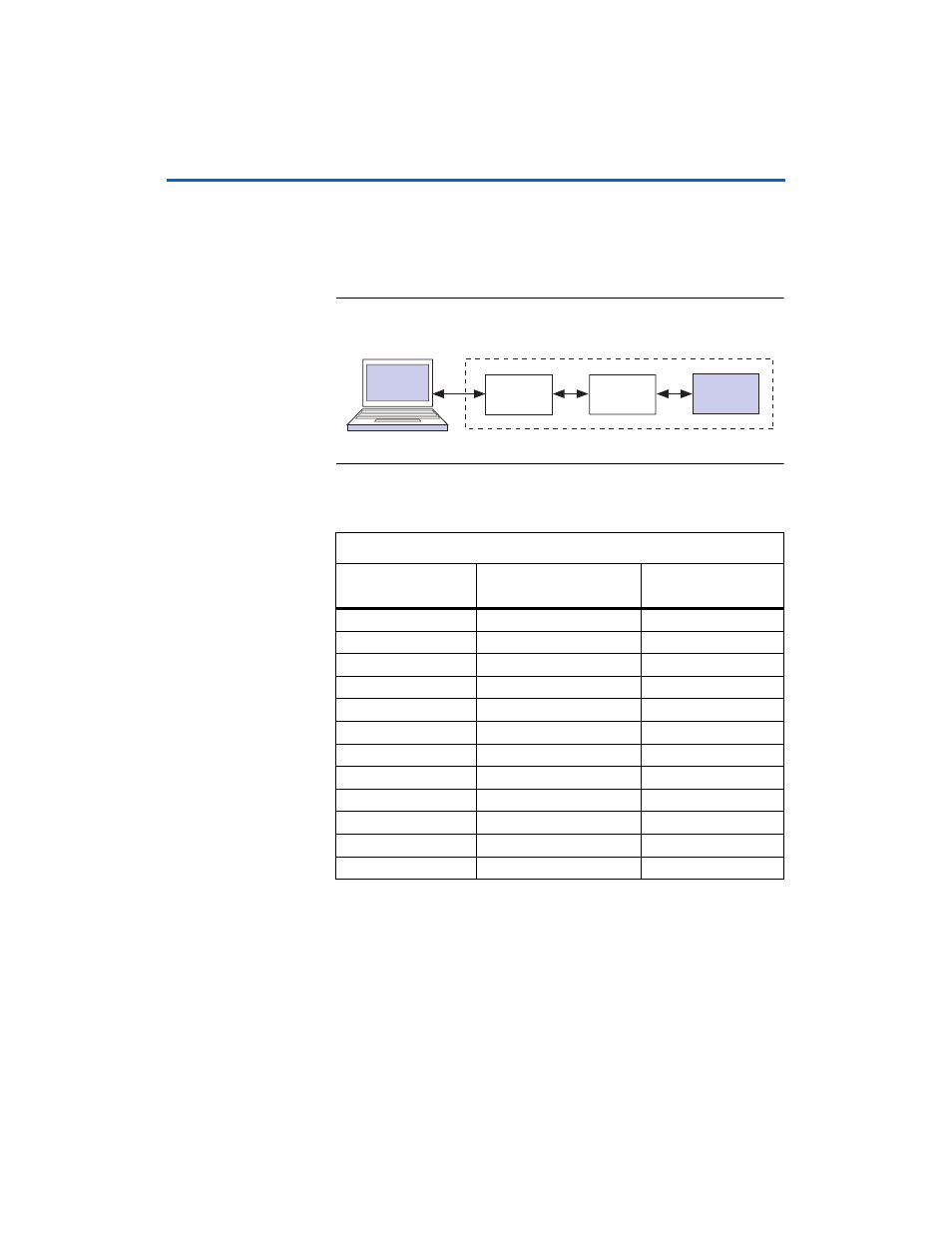

Figure 2–7. USB Interface to Stratix II GX Transceiver Signal Integrity

Development Board

Table 2–9

lists the USB interface to FPGA pinout.

Table 2–9. USB Interface to FPGA Pinout Table

USB Interface (U2)

Pin Number

Schematic Signal Name

Stratix II GX (U20)

Pin Number

40

UART_DATA0

F30

39

UART_DATA1

G31

38

UART_DATA2

D33

37

UART_DATA3

D32

36

UART_DATA4

H29

35

UART_DATA5

G30

33

UART_DATA6

E32

32

UART_DATA7

E31

30

UART_DATA8

J28

29

UART_DATA9

K27

28

UART_DATA10

E34

27

UART_DATA11

D34

USB PHY

Connector

FT2232L

USB UART

Stratix II GX

De

v

ice