Altera Stratix II GX EP2SGX90 Transceiver Signal Integrity Development Board User Manual

Page 36

2–26

Reference Manual

Altera Corporation

Stratix II GX EP2SGX90 Transceiver Signal Integrity Development Board

May 2006

Power Supply

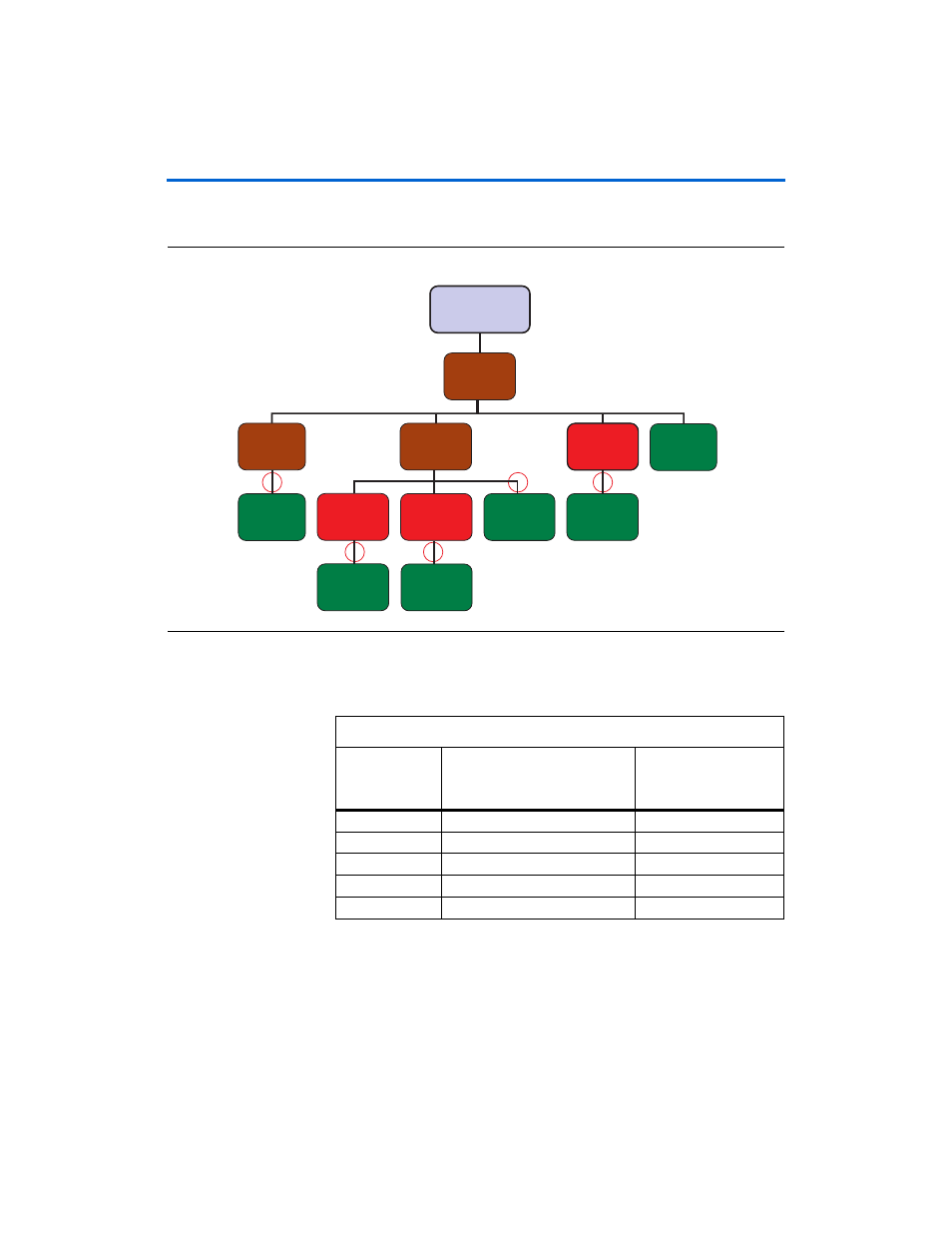

Figure 2–16

shows the board’s power supply block.

Figure 2–16. Power Supply Block Diagram

The decoupling analysis for this board is performed for a maximum

current consumption by the different power supplies, see

W

all AC/DC

Po

w

er S

u

pply

5-

V

to 1.2-

V

S

w

itches

5-

V

to 3.3-

V

S

w

itches

5-

V

to 3.3-

V

Linear

5-

V

Parts

16-

V

to 5-

V

S

w

itches

V

CCI

N

T

V

CCIO

and IC

3.3-

V

to

1.5-

V

Linear

3.3-

V

to

1.2-

V

Linear

GXB

and EPLL

Clock

and GXB

V

CCHTX

Table 2–20. Power Supply Pins & Maximum Current Consumption

Power Supply

Net Name in

Schematic

Power Supply Pins Connected in

Stratix II GX Device

Maximum Expected

Current Consumption

1V2

VCCINT and VCCP

4.75 A

VCCTX

VCCH

290 mA

1V2A

VCCR and VCCT

1.70 A

3V3

VCCIO and external components 2.45 A

3V3A

VCCA and external components

1.04 A