Hard ip reconfiguration interface, Hard ip reconfiguration interface -52 – Altera Arria 10 Avalon-ST User Manual

Page 118

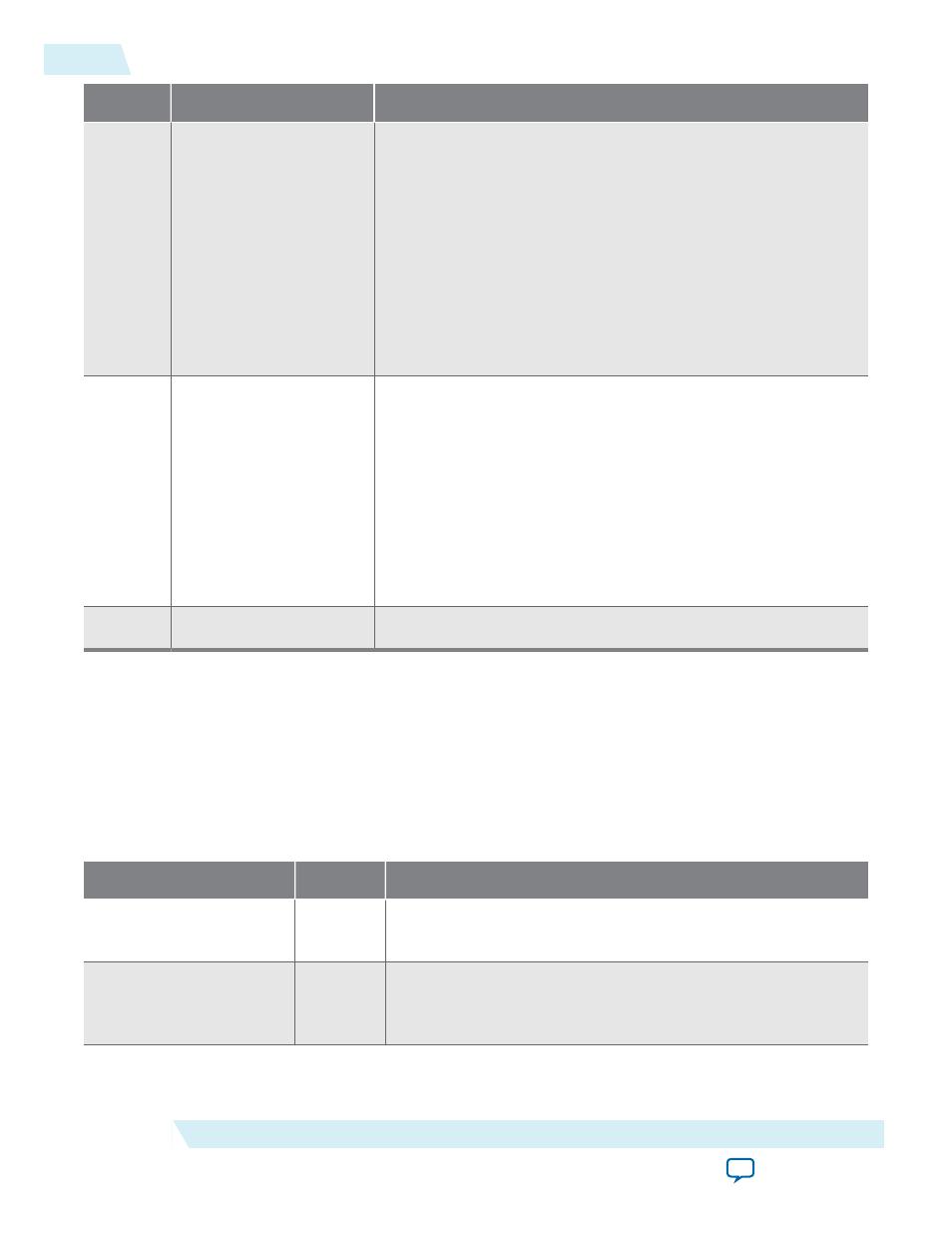

Bit(s)

Field

Description

[6:4]

multiple message

enable

This field indicates permitted values for MSI signals. For example,

if “100” is written to this field 16 MSI signals are allocated.

• 3’b000: 1 MSI allocated

• 3’b001: 2 MSI allocated

• 3’b010: 4 MSI allocated

• 3’b011: 8 MSI allocated

• 3’b100: 16 MSI allocated

• 3’b101: 32 MSI allocated

• 3’b110: Reserved

• 3’b111: Reserved

[3:1]

multiple message

capable

This field is read by system software to determine the number of

requested MSI messages.

• 3’b000: 1 MSI requested

• 3’b001: 2 MSI requested

• 3’b010: 4 MSI requested

• 3’b011: 8 MSI requested

• 3’b100: 16 MSI requested

• 3’b101: 32 MSI requested

• 3’b110: Reserved

[0]

MSI Enable

If set to 0, this component is not permitted to use MSI.

Hard IP Reconfiguration Interface

The Hard IP reconfiguration interface is an Avalon-MM slave interface with a 10-bit address and 16-bit

data bus. You can use this bus to dynamically modify the value of configuration registers that are read-

only at run time. To ensure proper system operation, reset or repeat device enumeration of the PCI

Express link after changing the value of read-only configuration registers of the Hard IP.

Table 6-18: Hard IP Reconfiguration Signals

Signal

Direction

Description

hip_reconfig_clk

Input

Reconfiguration clock. The frequency range for this clock is 100–

125 MHz.

hip_reconfig_rst_n

Input

Active-low Avalon-MM reset. Resets all of the dynamic reconfi‐

guration registers to their default values as described in Hard IP

Reconfiguration Registers.

6-52

Hard IP Reconfiguration Interface

UG-01145_avst

2015.05.04

Altera Corporation

Interfaces and Signal Descriptions