Link training, Link training -2 – Altera Arria 10 Avalon-ST User Manual

Page 260

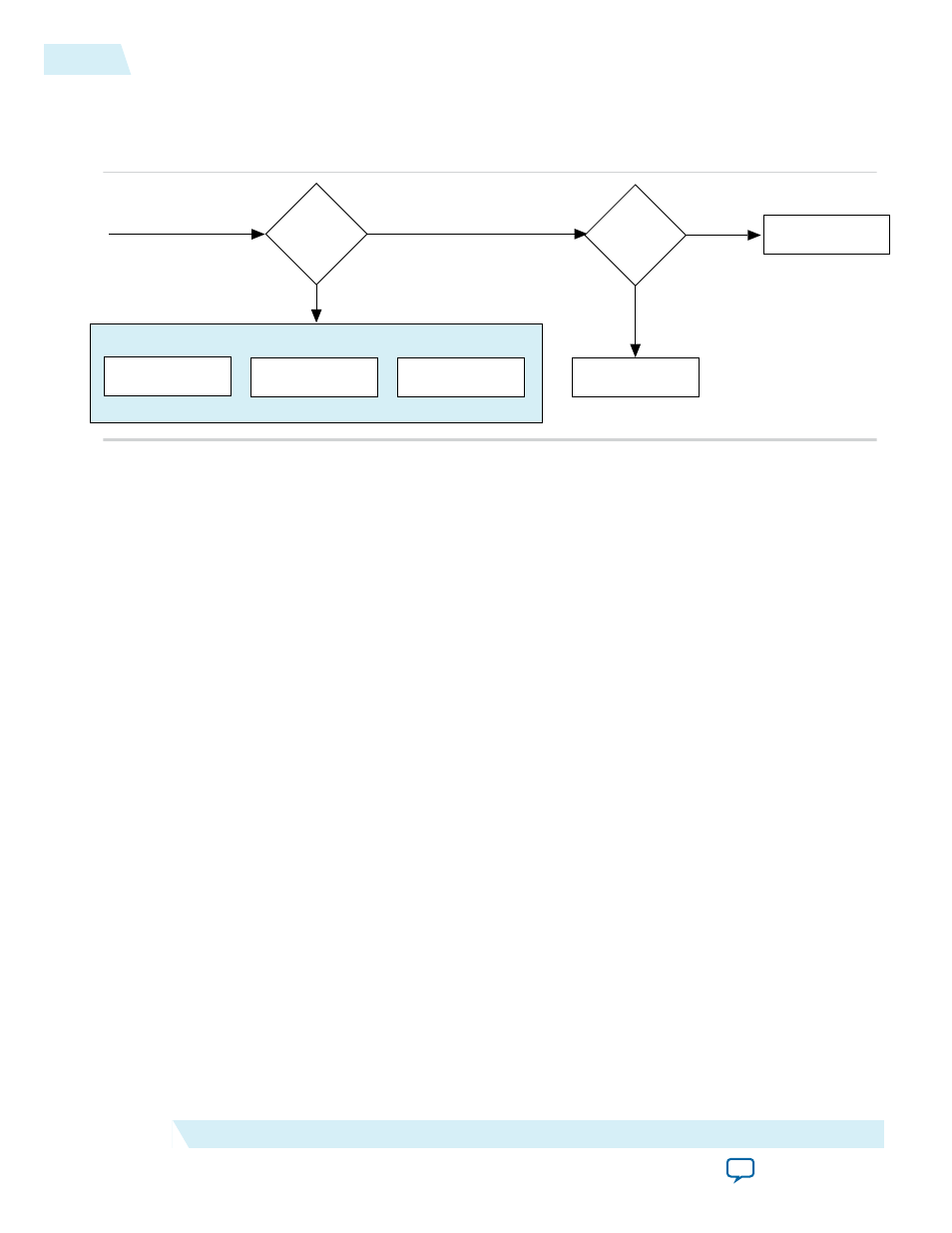

The following sections, describe how to debug the hardware bring-up flow. Altera recommends a

systematic approach to diagnosing bring-up issues as illustrated in the following figure.

Figure 18-1: Debugging Link Training Issues

No

system reset

Does Link

Train

Correctly?

Check PIPE

Interface

Use PCIe

Analyzer

Soft Reset System to

Force Enumeration

Check Configuration

Space

Check LTSSM

Status

Yes

Yes

No

Successful

OS/BIOS

Enumeration?

Link Training

The Physical Layer automatically performs link training and initialization without software intervention.

This is a well-defined process to configure and initialize the device's Physical Layer and link so that PCIe

packets can be transmitted. If you encounter link training issues, viewing the actual data in hardware

should help you determine the root cause. You can use the following tools to provide hardware visibility:

• SignalTap II Embedded Logic Analyzer

• Third-party PCIe analyzer

You can use SignalTap II Embedded Logic Analyzer to diagnose the LTSSM state transitions that are

occurring on the PIPE interface. The

ltssmstate[4:0]

bus encodes the status of LTSSM. The LTSSM

state machine reflects the Physical Layer’s progress through the link training process. For a complete

description of the states these signals encode, refer to Status, Link Training and Reset Signals. When link

training completes successfully and the link is up, the LTSSM should remain stable in the L0 state. When

link issues occur, you can monitor

ltssmstate[4:0]

to determine the cause.

Related Information

Reset, Status, and Link Training Signals

Debugging Link Failure in L0 Due To Deassertion of tx_st_ready

There are many reasons that link may stop transmitting data. The following table lists some possible

causes.

18-2

Link Training

UG-01145_avst

2015.05.04

Altera Corporation

Debugging