Altera Arria 10 Avalon-ST User Manual

Page 268

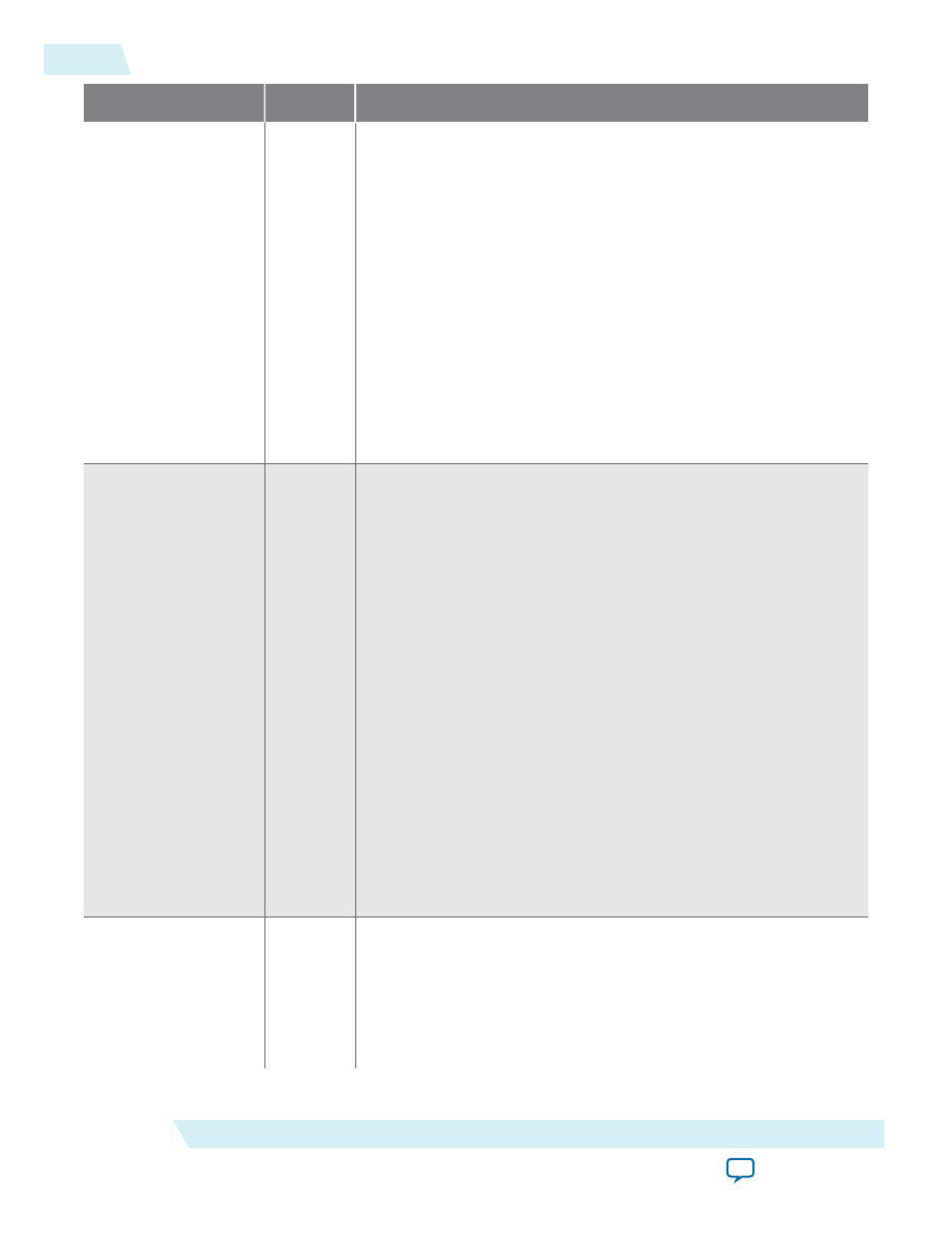

Date

Version

Changes Made

• Corrected width of

rx_st_sop

and

rx_st_eop

to 1 or two bits. If

you turn on Enable multiple packets per cycle these signals have

two bits; otherwise, they have one bit each. Refer to

• Removed non-existent signals

rx_st_bar1

and

rx_st_bar2

. If

you turn on Enable multiple packets per cycle, the IP core still

has only a single

rx_st_bar[7:0]

signal. Do not use this signal if

you turn on Enable multiple packets per cycle. Refer to

Avalon-ST RX Component Specific Signals

on page 6-4.

• Updated DUT module name in testbench and example design

figures.

on page 17-57.

• Fixed minor errors and typos.

2014.12.15

14.1

Made the following changes to the user guide:

• Added simulation log file,

altpcie_monitor_<dev>_dlhip_tlp_file_

log.log

in your simulation directory. Generation of the log file

requires the following simulation file,

<install_dir>altera/altera_pcie/

altera_pcie_a10_hip/altpcie_monitor_a10_dlhip_sim.sv

, that was not

present in earlier releases of the Quartus II software.

• Changed device part number for Getting Started chapter to

10AX115R2F40I2LG.

• Added statement that the bottom left hard IP block includes the

CvP functionality for flip chip packages. For other package types,

the CvP functionality is in the bottom right block.

• Removed 125 MHz clock as optional

refclk

frequency in Arria 10

devices. Arria 10 devices support an 100 MHz reference clock as

specified by the PCI Express Base Specification, Rev 3.0.

• Corrected bit definitions for

CvP Status

register.

• Updated definition of

CVP_NUMCLKS

in the

CvP Mode Control

register.

• Added definitions for

test_in[2]

,

test_in[6]

and

test_in[7]

.

• Enhanced instructions Compiling the Design to include steps

necessary to download to Altera development kits.

2014.08.18

14.0a10

Made the following changes to the Arria 10 Hard IP for PCI Express:

• Changed the PIPE interface to 32 bits for all data rates. This

change requires you to recompile your 13.1 variant in 14.0.

• Made fPLL available as the TX PLL for all data rates. This change

allows you to use the ATX PLLs for higher data rate protocols if

necessary.

C-2

Revision History for the Avalon-ST Interface

UG-01145_avst

2015.05.04

Altera Corporation

Additional Information