Arria 10 features, Arria 10 features -2 – Altera Arria 10 Avalon-ST User Manual

Page 9

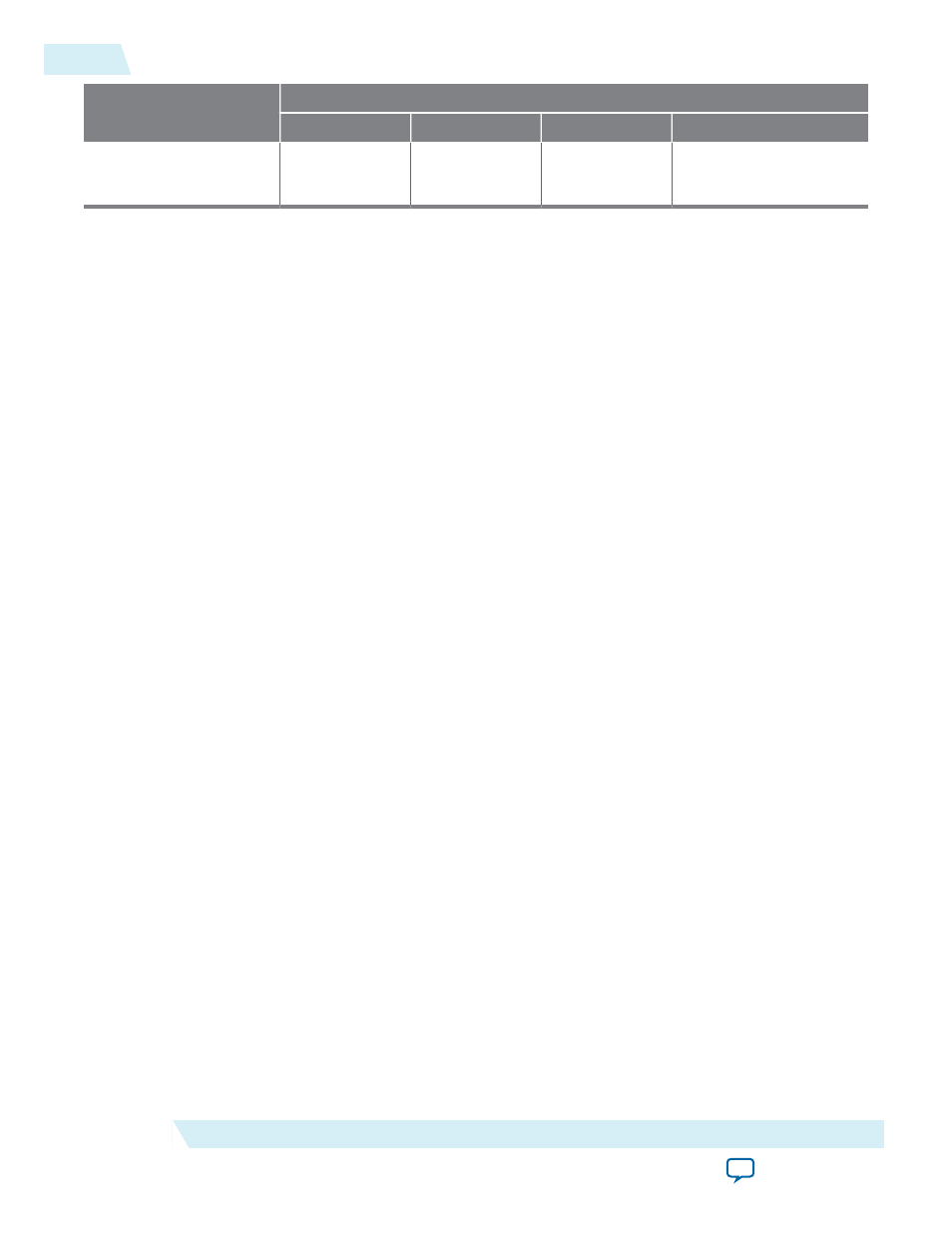

Link Width

×1

×2

×4

×8

PCI Express Gen3

(8.0 Gbps)

7.87

15.75

31.51

63

Refer to the AN 456: PCI Express High Performance Reference Design for more information about

calculating bandwidth for the hard IP implementation of PCI Express in many Altera FPGAs, including

the Arria 10 Hard IP for PCI Express IP core.

Devices

Related Information

•

•

•

Arria 10 Features

New features in the Quartus

®

II 15.0 software release:

• Added Enable Altera Debug Master Endpoint (ADME) parameter to support optional Native PHY

register programming with the Altera System Console.

The Arria 10 Hard IP for PCI Express supports the following features:

• Complete protocol stack including the Transaction, Data Link, and Physical Layers implemented as

hard IP.

• Support for ×1, ×2, ×4, and ×8 configurations with Gen1, Gen2, or Gen3 lane rates for Root Ports and

Endpoints.

• Dedicated 16 KByte receive buffer.

• Optional support for Configuration via Protocol (CvP) using the PCIe link allowing the I/O and core

bitstreams to be stored separately.

• Qsys example designs demonstrating parameterization, design modules, and connectivity.

• Extended credit allocation settings to better optimize the RX buffer space based on application type.

• Support for multiple packets per cycle with the 256-bit Avalon-ST interface.

• Optional end-to-end cyclic redundancy code (ECRC) generation and checking and advanced error

reporting (AER) for high reliability applications.

• Easy to use:

• Flexible configuration.

• Substantial on-chip resource savings and guaranteed timing closure.

• No license requirement.

• Example designs to get started.

1-2

Arria 10 Features

UG-01145_avst

2015.05.04

Altera Corporation

Datasheet