Altera Arria 10 Avalon-ST User Manual

Page 98

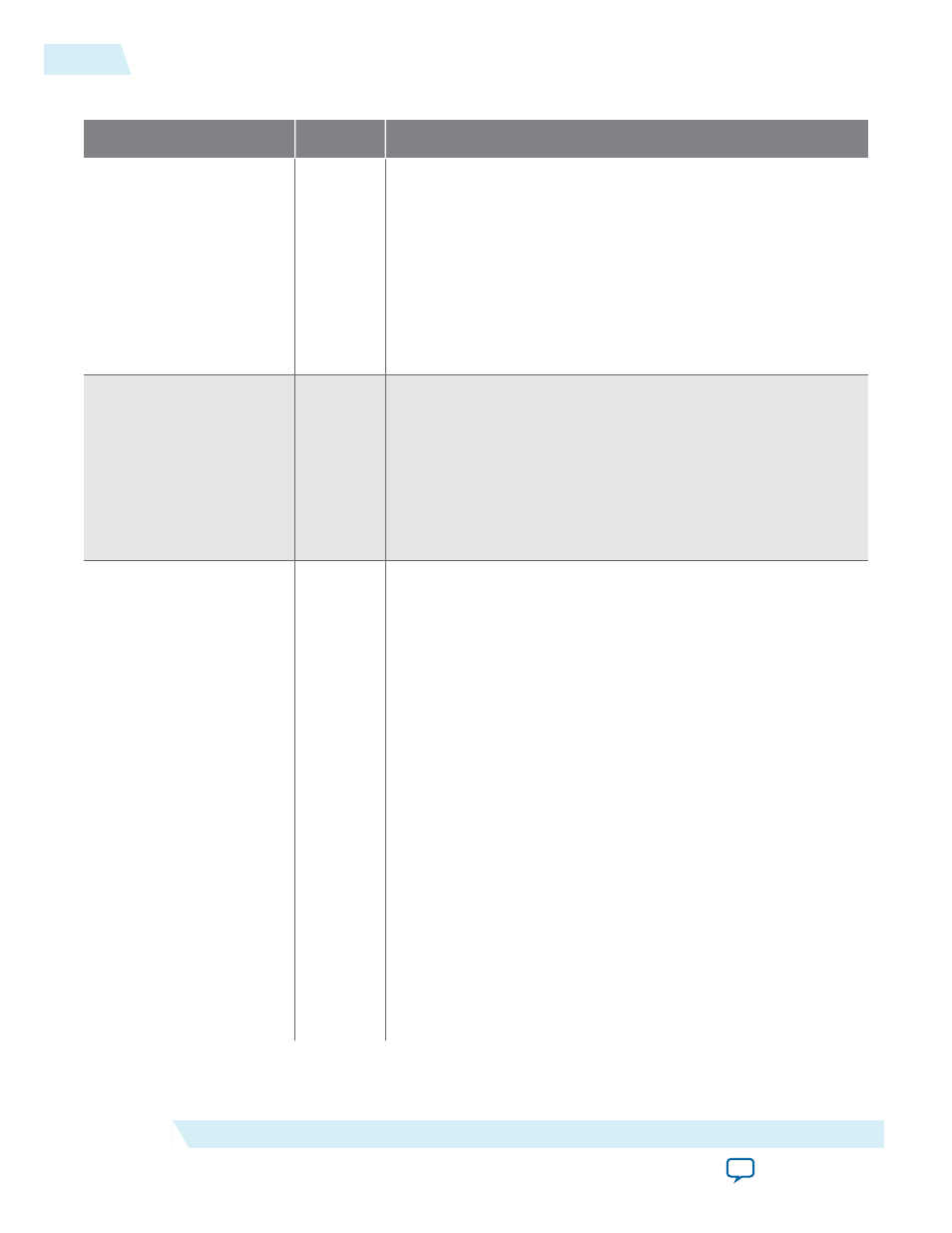

Table 6-6: Reset Signals

Signal

Direction

Description

npor

Input

Active low reset signal. In the Altera hardware example designs,

npor

is the

OR

of

pin_perst

and

local_rstn

coming from the

software Application Layer. If you do not drive a soft reset signal

from the Application Layer, this signal must be derived from

pin_perst

. You cannot disable this signal. Resets the entire IP

Core and transceiver. Asynchronous.

This signal is edge, not level sensitive; consequently, you cannot

use a low value on this signal to hold custom logic in reset. For

more information about the reset controller, refer to Reset.

reset_status

Output

Active high reset status signal. When asserted, this signal

indicates that the Hard IP clock is in reset. The

reset_status

signal is synchronous to the

pld_clk

clock and is deasserted only

when the

npor

is deasserted and the Hard IP for PCI Express is

not in reset (

reset_status_hip

= 0). You should use

reset_

status

to drive the reset of your application. This reset is used

for the Hard IP for PCI Express IP Core with the Avalon-ST

interface.

pin_perst

Input

Active low reset from the PCIe reset pin of the device.

pin_perst

resets the datapath and control registers. Configuration via

Protocol (CvP) requires this signal. For more information about

CvP refer to Configuration via Protocol (CvP).

Arria 10 devices can have up to 4 instances of the Hard IP for

PCI Express. Each instance has its own

pin_perst

signal. You

must connect the

pin_perst

of each Hard IP instance to the

corresponding

nPERST

pin of the device. These pins have the

following locations:

•

NPERSTL0

: bottom left Hard IP and CvP blocks

•

NPERSTL1

: top left Hard IP block

•

NPERSTR0

: bottom right Hard IP block

•

NPERSTR1

: top right Hard IP block

For example, if you are using the Hard IP instance in the bottom

left corner of the device, you must connect

pin_perst

to

NPERSL0

.

For maximum use of the Arria 10 device, Altera recommends

that you use the bottom left Hard IP first. This is the only

location that supports CvP over a PCIe link. If your design does

not require CvP, you may select other Hard IP blocks.

6-32

Reset, Status, and Link Training Signals

UG-01145_avst

2015.05.04

Altera Corporation

Interfaces and Signal Descriptions