Altera Arria 10 Avalon-ST User Manual

Page 90

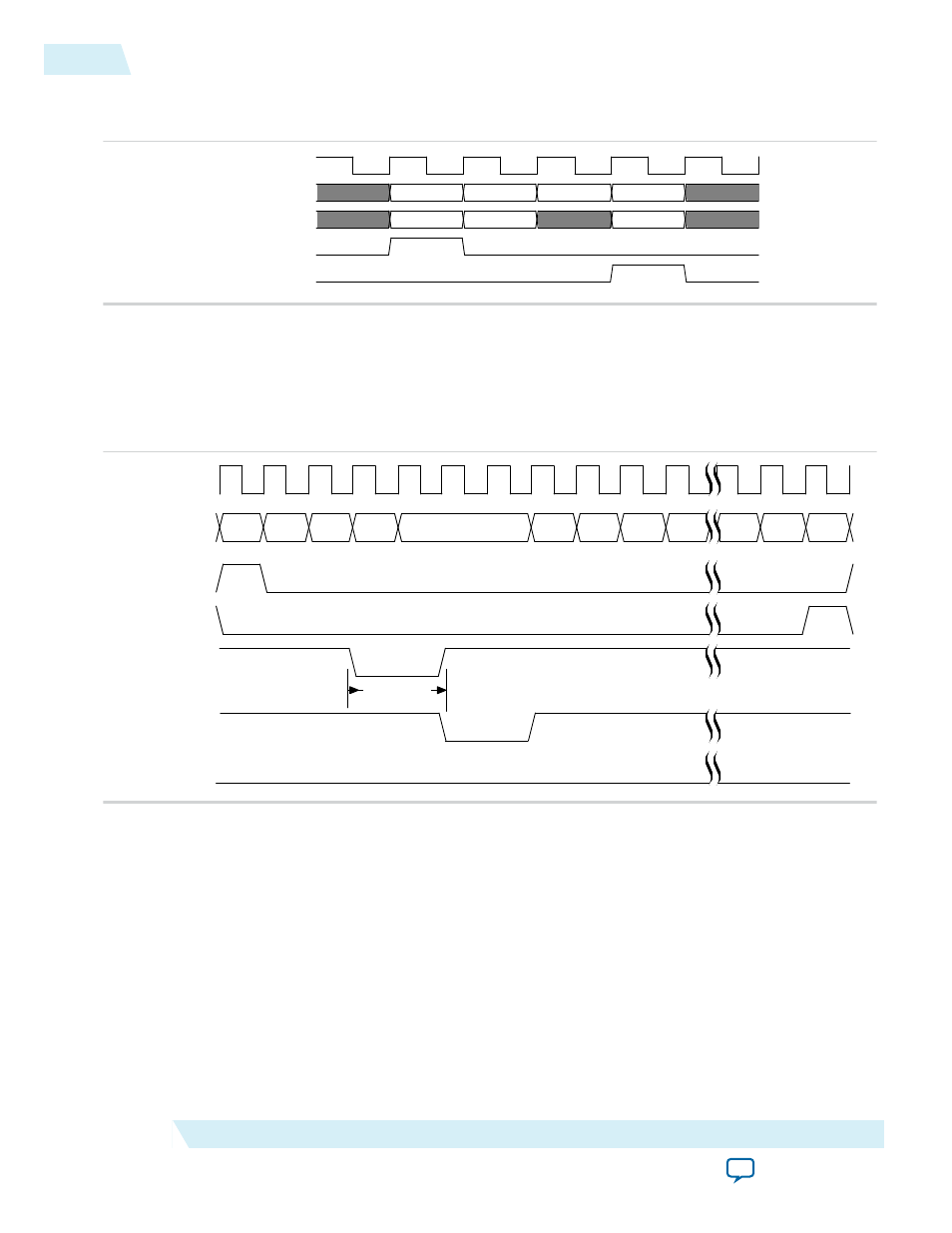

Figure 6-21: 64-Bit Avalon-ST tx_st_data Cycle Definition for TLP 4-Dword Header with Non-Qword

Aligned Address

pld_clk

tx_st_data[63:32]

tx_st_data[31:0]

tx_st_sop

tx_st_eop

Header 1

Header3

Data0

Data2

Header 0

Header2

Data1

Figure 6-22: 64-Bit Transaction Layer Backpressures the Application Layer

The following figure illustrates the timing of the TX interface when the Arria 10 Hard IP for PCI Express

pauses transmission by the Application Layer by deasserting

tx_st_ready

. Because the

readyLatency

is

two cycles, the Application Layer deasserts

tx_st_valid

after two cycles and holds

tx_st_data

until two

cycles after

tx_st_ready

is asserted.

coreclkout

tx_st_sop

tx_st_eop

tx_st_ready

tx_st_valid

tx_st_err

tx_st_data[63:0]

.

.

.

.

.

.

.

.

.

.

readyLatency

00. . 00 ...

BB...

BB ...

BBBB0306BBB0305

BB...

BB..

BB ...

BB ...

BB ... BB ...

BB... .

6-24

Data Alignment and Timing for the 64‑Bit Avalon-ST TX Interface

UG-01145_avst

2015.05.04

Altera Corporation

Interfaces and Signal Descriptions