Figure, Scc/escc user manual – Zilog Z80230 User Manual

Page 50

SCC/ESCC

User Manual

UM010903-0515

Interfacing the SCC/ESCC

43

some action taken by the processor. The external daisy chain may be controlled by the DLC bit in

WR9. This bit, when set, forces IEO Low, disabling all lower priority devices.

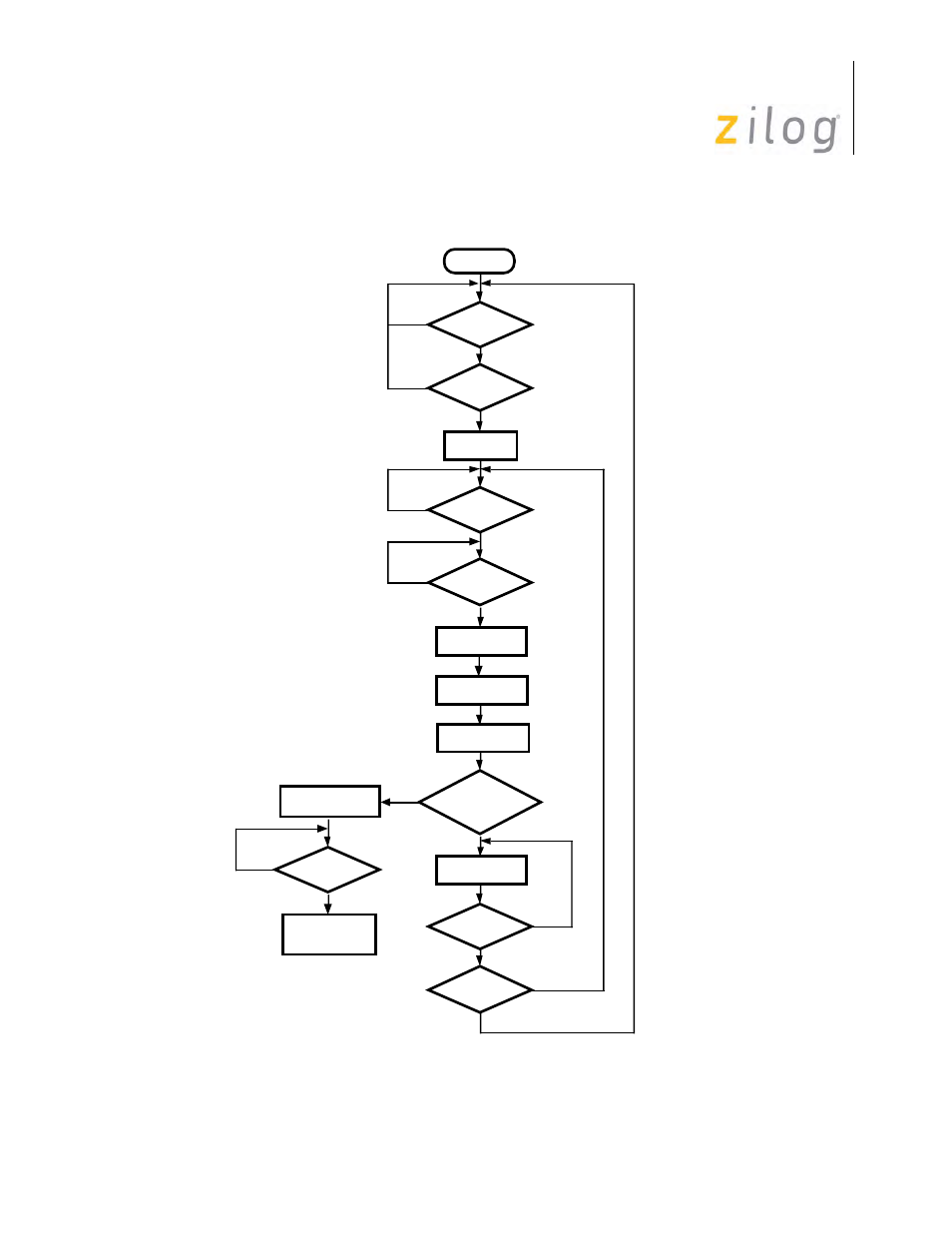

Interrupt Flow Chart (for each interrupt source)

Start

Interrupt Pendi

Set (IP=1)

Master

Interrupt Enable

(MIE=1)?

Is Peripheral

Enable Pin Ac

(IEI=H)?

Yes

Unit Selected for CPU

Service (IUS=1)

Interrupt

Condition

Exits?

Specific

Interrupt Enabl

(IEx=1)?

Peripheral Request

Interrupt (INT=L)

IEI/IEO Daisy Chain

Settles (Wait for DS

CPU Initiates Statu

Decode (INTACK=L

Has Higher

Priority Periphera

Disabled Unit?

(IEI=L)

Yes

CPU Services High

Priority Periphera

Priority

Service

Complete?

Interrupt Still

Pending (IP=1)

?

Service

Routine Comple

?

Yes

(Option) Check Oth

Internal IP, Bits,

RESET IUS and Ex

No

Yes

Yes

No

No

No

Yes

Yes

No

No

No

No

Yes