Zilog Z80230 User Manual

Page 68

SCC/ESCC

User Manual

UM010903-0515

Interfacing the SCC/ESCC

61

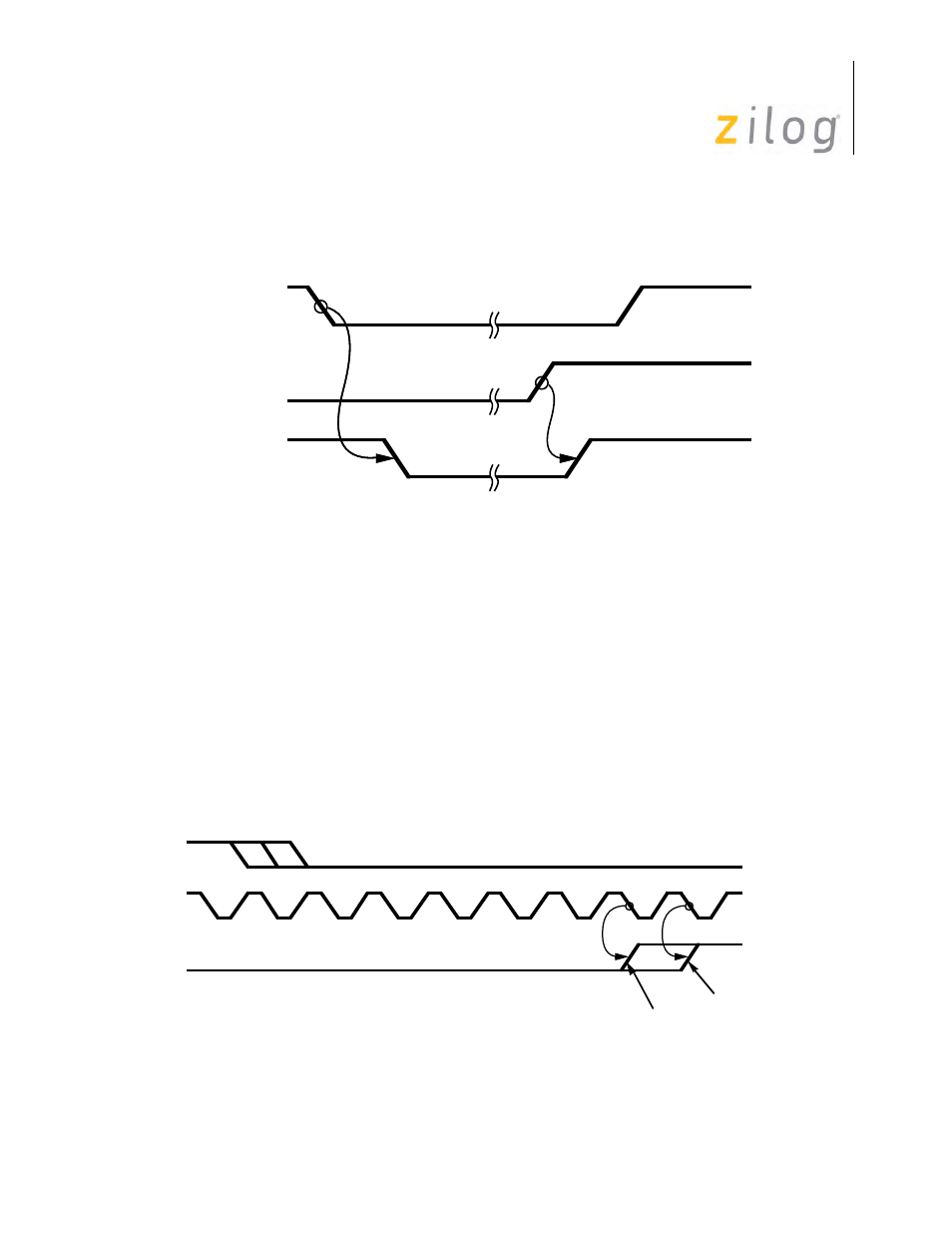

Wait On Transmit Timing

This allows the use of a block move instruction to transfer the transmit data. In the case of the

Z80X30, /WAIT will go active in response to /DS going active, but only if WR8 is being accessed

and a write is attempted. In all other cases, /WAIT remains open-drain. In the case of the Z85X30,

/WAIT goes active in response to /WR going active, but only if the data buffer is being accessed,

either directly or via the pointers. The /WAIT pin is released in response to the falling edge of

PCLK. Details of the timing are displayed in

Care must be taken when using this function, particularly at slow transmission speed. The /WAIT

pin stays active as long as the transmit buffer stays full, so there is a possibility that the CPU may

be kept waiting for a long period.

Wait on Transmit Timing (ii)

/DS or /WR

to Tx Buffer

Tx Buffer Empty

/W//REQ

(=WAIT)

Empty

Full

/TRxC

/WAIT

SYNC Modes

PCLK

ASYNC Modes