Zilog Z80230 User Manual

Page 64

SCC/ESCC

User Manual

UM010903-0515

Interfacing the SCC/ESCC

57

are closed. If the master enable for the External/Status interrupts is not set, the IP is never set, even

though the latches may be present in the signal paths and working as described.

RR0 External/Status Interrupt Operation

Because the latches close on the current status, but give no indication of change, the processor

must maintain a copy of RR0 in memory. When the SCC generates an External/Status Interrupt,

the processor should read RR0 and determine which condition changed state and take appropriate

action. The copy of RR0 in memory is then updated and the Reset External/Status Interrupt com-

mand issued. Care must be taken in writing the interrupt service routine for the External/Status

interrupts because it is possible for more than one status condition to change state at the same

time. All of the latch bits in RR0 should be compared to the copy of RR0 in memory. If none have

changed and the ZC interrupt is enabled, the Zero Count condition caused the interrupt.

On the ESCC, the contents of RR0 are latched while reading this register. The ESCC prevents the

contents of RR0 from changing while the read cycle is active. On the NMOS/CMOS version, it is

possible for the status of RR0 to change while a read is in progress, so it is necessary to read RR0

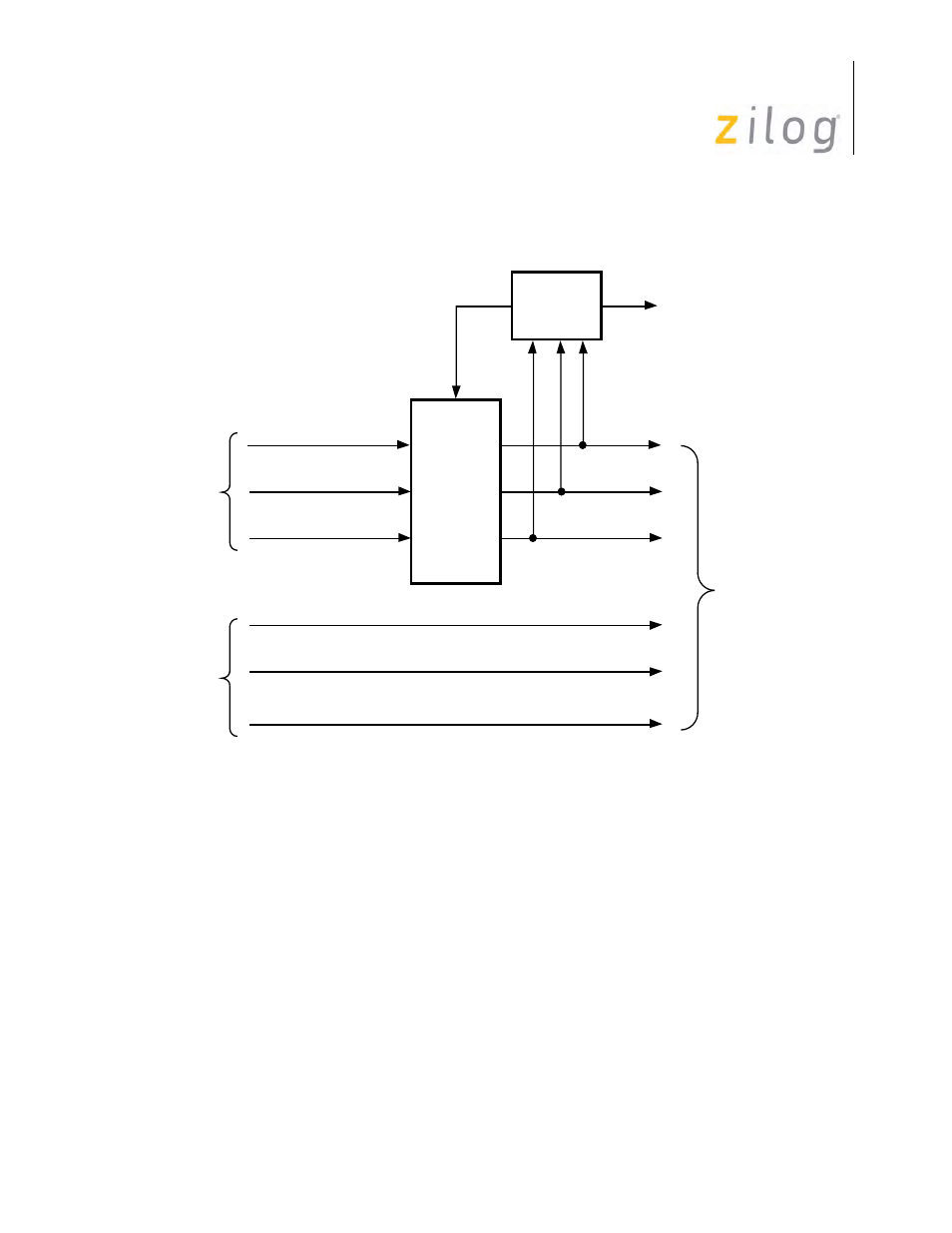

External/St

Condition

wit

IE =

Latch

Change

Detecto

External/St

Condition

wit

IE =

To IP

To RR