Altera MAX 10 Embedded Memory User Manual

Page 12

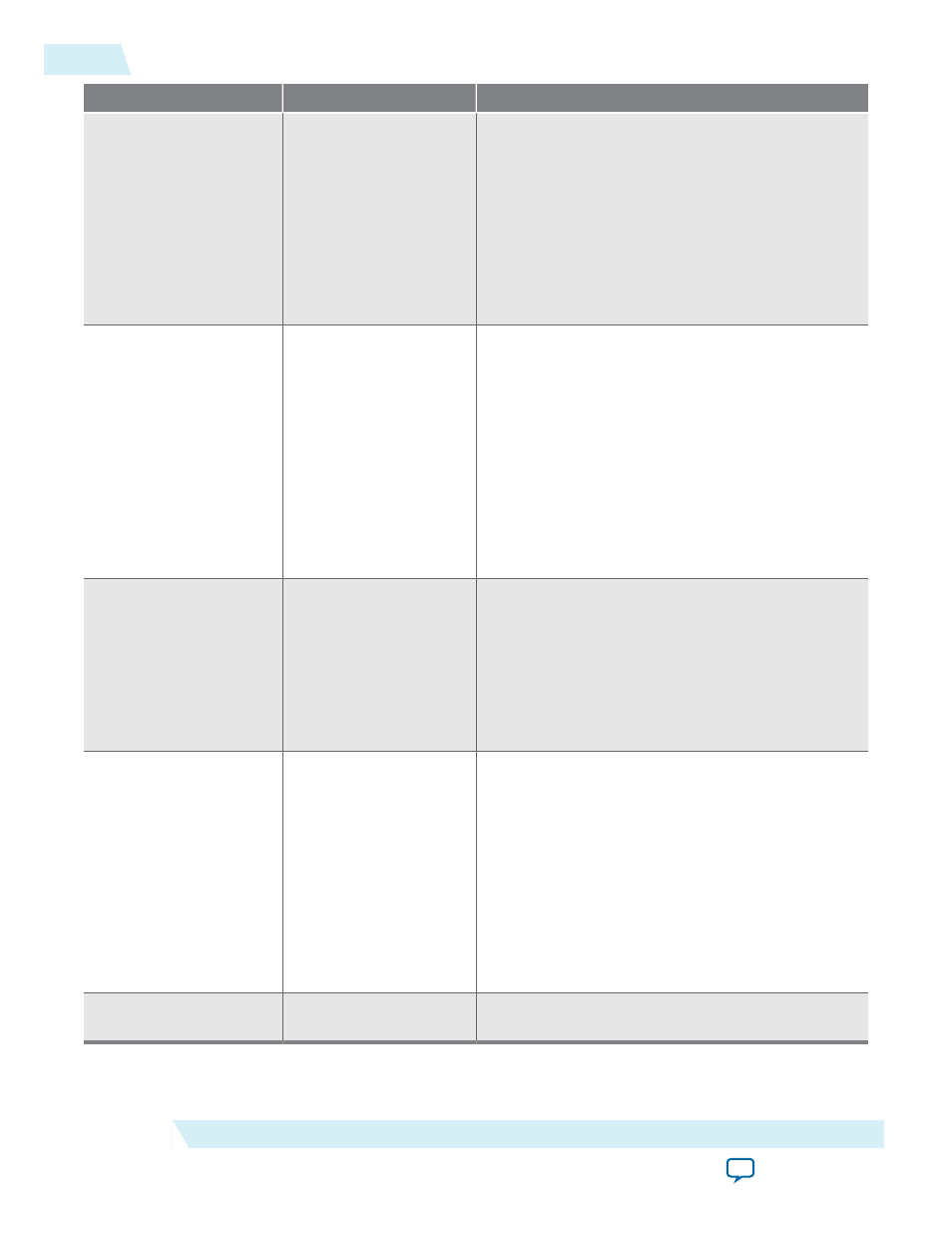

Memory Operation Mode

Related IP Core

Description

Single-port ROM

ROM: 1-PORT IP Core

Only one address port is available for read

operation.

You can use the memory blocks as a ROM.

• Initialize the ROM contents of the memory

blocks using a .mif or .hex file.

• The address lines of the ROM are registered.

• The outputs can be registered or unregistered.

• The ROM read operation is identical to the read

operation in the single-port RAM configuration.

Dual-port ROM

ROM: 2-PORT IP Core

The dual-port ROM has almost similar functional

ports as single-port ROM. The difference is dual-

port ROM has an additional address port for read

operation.

You can use the memory blocks as a ROM.

• Initialize the ROM contents of the memory

blocks using a .mif or .hex file.

• The address lines of the ROM are registered.

• The outputs can be registered or unregistered.

• The ROM read operation is identical to the read

operation in the single-port RAM configuration.

Shift-register

Shift Register (RAM-

based) IP Core

You can use the memory blocks as a shift-register

block to save logic cells and routing resources.

The input data width (w), the length of the taps (m),

and the number of taps (n) determine the size of a

shift register (w × m × n).

You can cascade memory blocks to implement

larger shift registers.

FIFO

FIFO IP Core

You can use the memory blocks as FIFO buffers.

• Use the FIFO IP core in single clock FIFO

(SCFIFO) mode and dual clock FIFO (DCFIFO)

mode to implement single- and dual-clock FIFO

buffers in your design.

• Use dual clock FIFO buffers when transferring

data from one clock domain to another clock

domain.

• The M9K memory blocks do not support

simultaneous read and write from an empty

FIFO buffer.

Memory-based

multiplier

ALTMEMMULT IP Core You can use the memory blocks as a memory-based

multiplier.

2-8

Supported Memory Operation Modes

UG-M10MEMORY

2015.05.04

Altera Corporation

MAX 10 Embedded Memory Architecture and Features