Altera MAX 10 Embedded Memory User Manual

Page 57

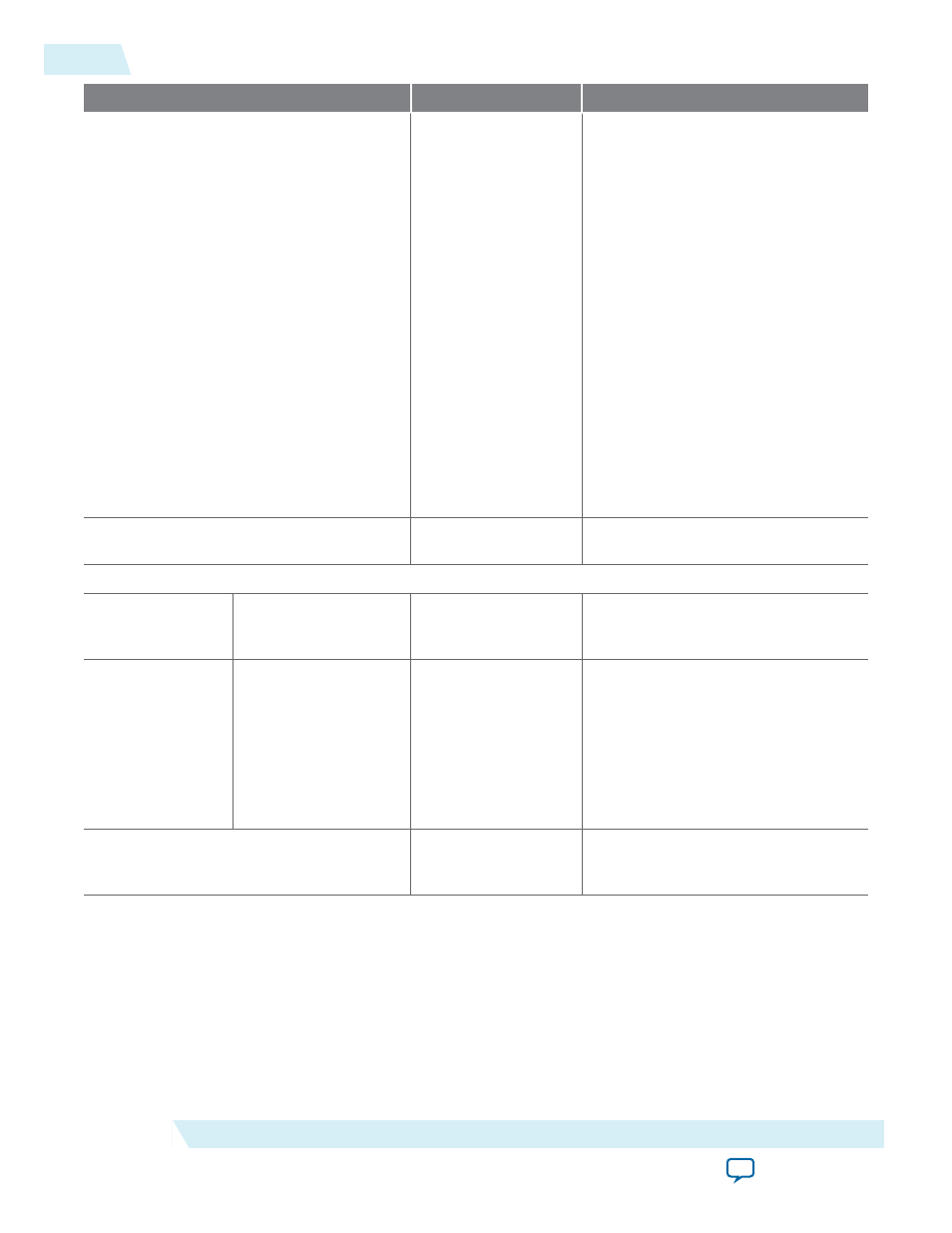

Option

Legal Values

Description

What clocking method would you like to

use?

• Single clock

• Dual clock: use

separate ‘input’ and

‘output’ clocks

• Dual clock: use

separate clocks for

A and B ports

Specifies the clocking method to use.

• Single clock—A single clock and

a clock enable controls all

registers of the memory block.

• Dual Clock: use separate ‘input’

and ‘output’ clocks—An input

and an output clock controls all

registers related to the data input

and output to/from the memory

block including data, address,

byte enables, read enables, and

write enables.

• Dual clock: use separate clocks

for A and B ports—Clock A

controls all registers on the port

A side; clock B controls all

registers on the port B side. Each

port also supports independent

clock enables for both port A and

port B registers, respectively.

Create a ‘rden_a’ and 'rden_b' read enable

signal

On/Off

Specifies whether to create read

enable signals.

Parameter Settings: Regs/Clkens/Aclrs

Which ports

should be

registered?

• Write input ports

• Read output port(s)

On/Off

Specifies whether to register the read

or write input and output ports.

More Options

• Input ports

• 'address_a' port

• 'address_b' port

• Q output ports

• ‘q_a’ port

• 'q_b' port

On/Off

The read and write input ports are

turned on by default. You only need

to specify whether to register the Q

output ports.

Create one clock enable signal for each

clock signal.

On/Off

Specifies whether to turn on the

option to create one clock enable

signal for each clock signal.

7-6

ROM:2-Port IP Core Parameters For MAX 10 Devices

UG-M10MEMORY

2015.05.04

Altera Corporation

ROM: 2-PORT IP Core References