Consider power-up state and memory initialization, Control clocking to reduce power consumption, Control clocking to reduce power consumption -5 – Altera MAX 10 Embedded Memory User Manual

Page 21

Consider Power-Up State and Memory Initialization

Consider the power-up state of the different types of memory blocks if you are designing logic that

evaluates the initial power-up values, as listed in the following table:

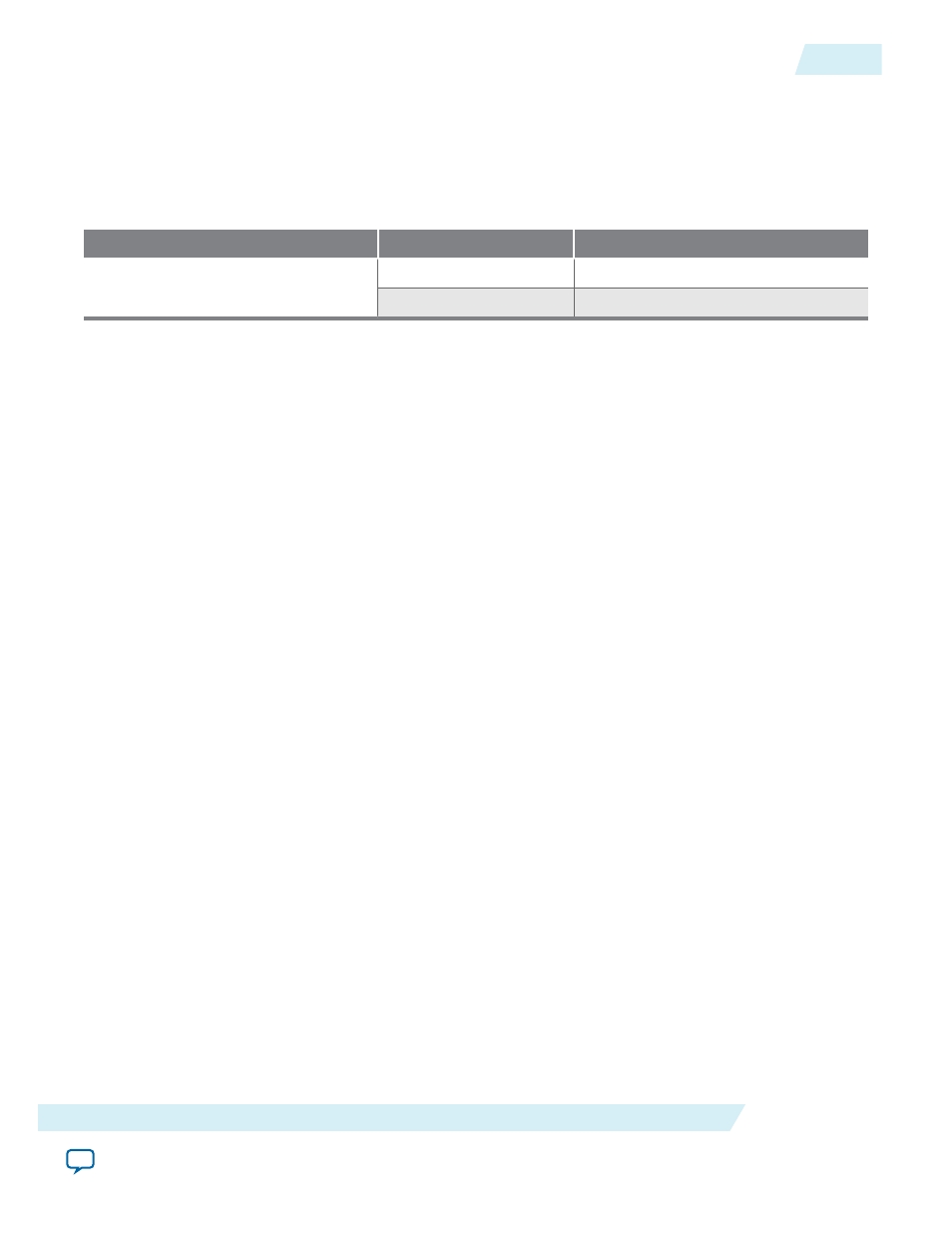

Table 3-3: Initial Power-Up Values of Embedded Memory Blocks

Memory Type

Output Registers

Power Up Value

M9K

Used

Zero (cleared)

Bypassed

Zero (cleared)

By default, the Quartus II software initializes the RAM cells to zero unless you specify a .mif.

All memory blocks support initialization with a .mif. You can create .mif files in the Quartus II software

and specify their use with the RAM IP when you instantiate a memory in your design. Even if a memory is

preinitialized (for example, using a .mif), it still powers up with its output cleared. Only the subsequent

read after power up outputs the preinitialized values.

Only the following MAX 10 configuration modes support memory initialization:

• Single Compressed Image with Memory Initialization

• Single Uncompressed Image with Memory Initialization

Related Information

Provides more information about selecting MAX 10 internal configuration modes.

Control Clocking to Reduce Power Consumption

Reduce AC power consumption in your design by controlling the clocking of each memory block:

• Use the read-enable signal to ensure that read operations occur only when necessary. If your design

does not require read-during-write, you can reduce your power consumption by deasserting the read-

enable signal during write operations, or during the period when no memory operations occur.

• Use the Quartus II software to automatically place any unused memory blocks in low-power mode to

reduce static power.

• Create independent clock enable for different input and output registers to control the shut down of a

particular register for power saving purposes. From the parameter editor, click More Options (beside

the clock enable option) to set the available independent clock enable that you prefer.

Related Information

MAX 10 Embedded Memory Clock Modes

on page 2-9

UG-M10MEMORY

2015.05.04

Consider Power-Up State and Memory Initialization

3-5

MAX 10 Embedded Memory Design Consideration

Altera Corporation