Altera MAX 10 Embedded Memory User Manual

Page 67

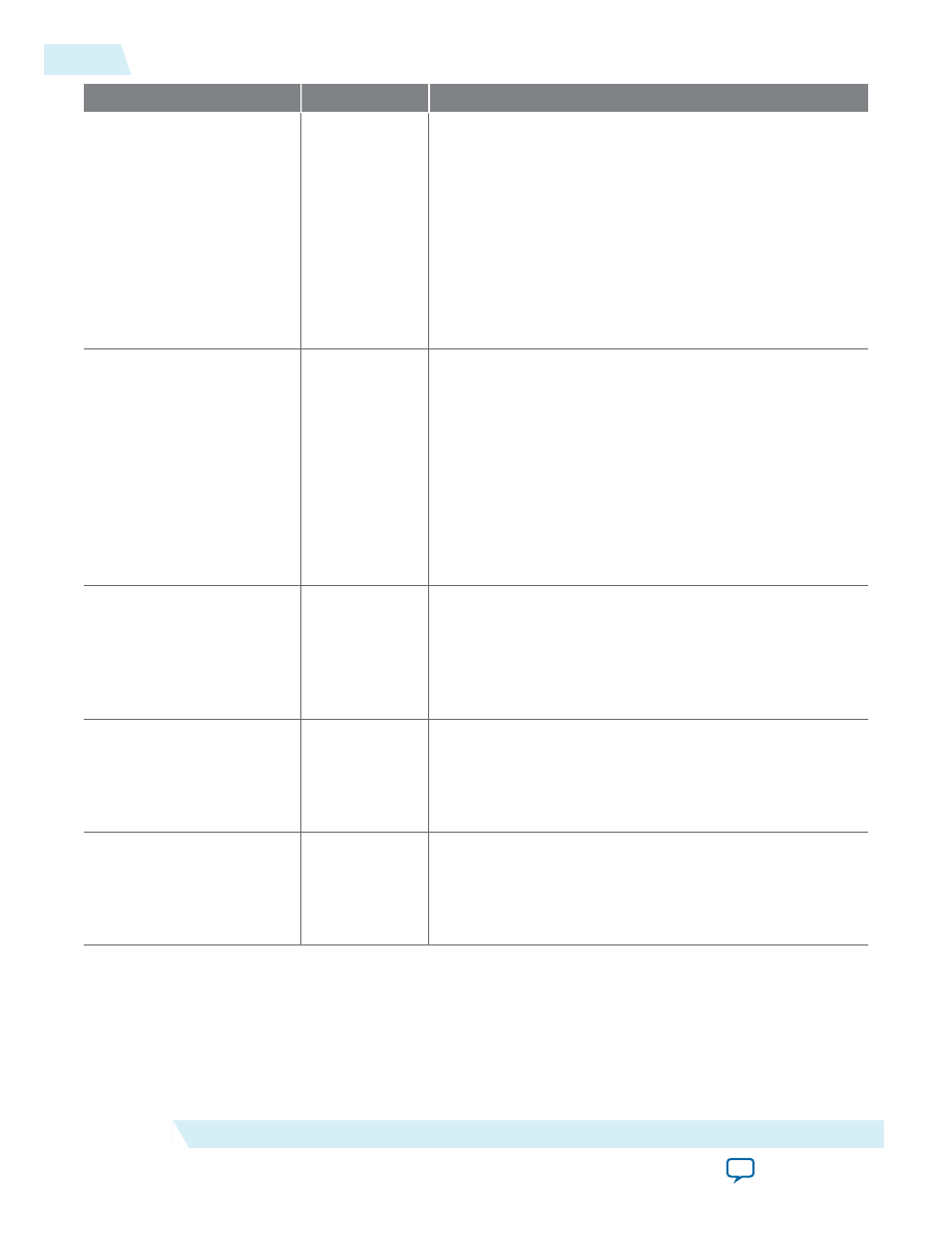

Parameter

HDL Parameter

Description

How many sync stages?

(2)

rdsync_

delaypipe

Specifies the number of synchronization stages in the cross

clock domain. The value of the rdsync_delaypipe

parameter relates the synchronization stages from the

write control logic to the read control logic; the wrsync_

delaypipe parameter relates the synchronization stages

from the read control logic to the write control logic. Use

these parameters to set the number of synchronization

stages if the clocks are not synchronized, and set the

clocks_are_synchronized parameter to FALSE. The actual

synchronization stage implemented relates variously to the

parameter value assigned, depends on the target device.

How many sync stages?

(2)

wrsync_

delaypipe

Specifies the number of synchronization stages in the cross

clock domain. The value of the rdsync_delaypipe

parameter relates the synchronization stages from the

write control logic to the read control logic; the wrsync_

delaypipe parameter relates the synchronization stages

from the read control logic to the write control logic. Use

these parameters to set the number of synchronization

stages if the clocks are not synchronized, and set the

clocks_are_synchronized parameter to FALSE. The actual

synchronization stage implemented relates variously to the

parameter value assigned, depends on the target device.

Implement FIFO storage

with logic cells only, even

if the device contains

memory blocks.

use_eab

Specifies whether or not the FIFO IP core is constructed

using RAM blocks. This parameter is disabled by default. If

you turn off this parameter, the FIFO IP core is

implemented in logic elements, regardless of the memory

block type assigned to the What should the memory block

type be parameter.

Add circuit to

synchronize ‘aclr’ input

with ‘wrclk’

(2)

write_aclr_

synch

Specifies whether or not to add a circuit that causes the

aclr

port to be internally synchronized by the

wrclk

clock. Adding the circuit prevents the race condition

between the

wrreq

and

aclr

ports that could corrupt the

FIFO IP core. This parameter is disabled by default.

Add circuit to

synchronize ‘aclr’ input

with ‘rdclk’

read_aclr_

synch

Specifies whether or not to add a circuit that causes the

aclr

port to be internally synchronized by the

rdclk

clock. Adding the circuit prevents the race condition

between the

rdreq

and

aclr

ports that could corrupt the

FIFO IP core. This parameter is disabled by default.

9-6

FIFO IP Core Parameters for MAX 10 Devices

UG-M10MEMORY

2015.05.04

Altera Corporation

FIFO IP Core References