Altera MAX 10 Embedded Memory User Manual

Page 66

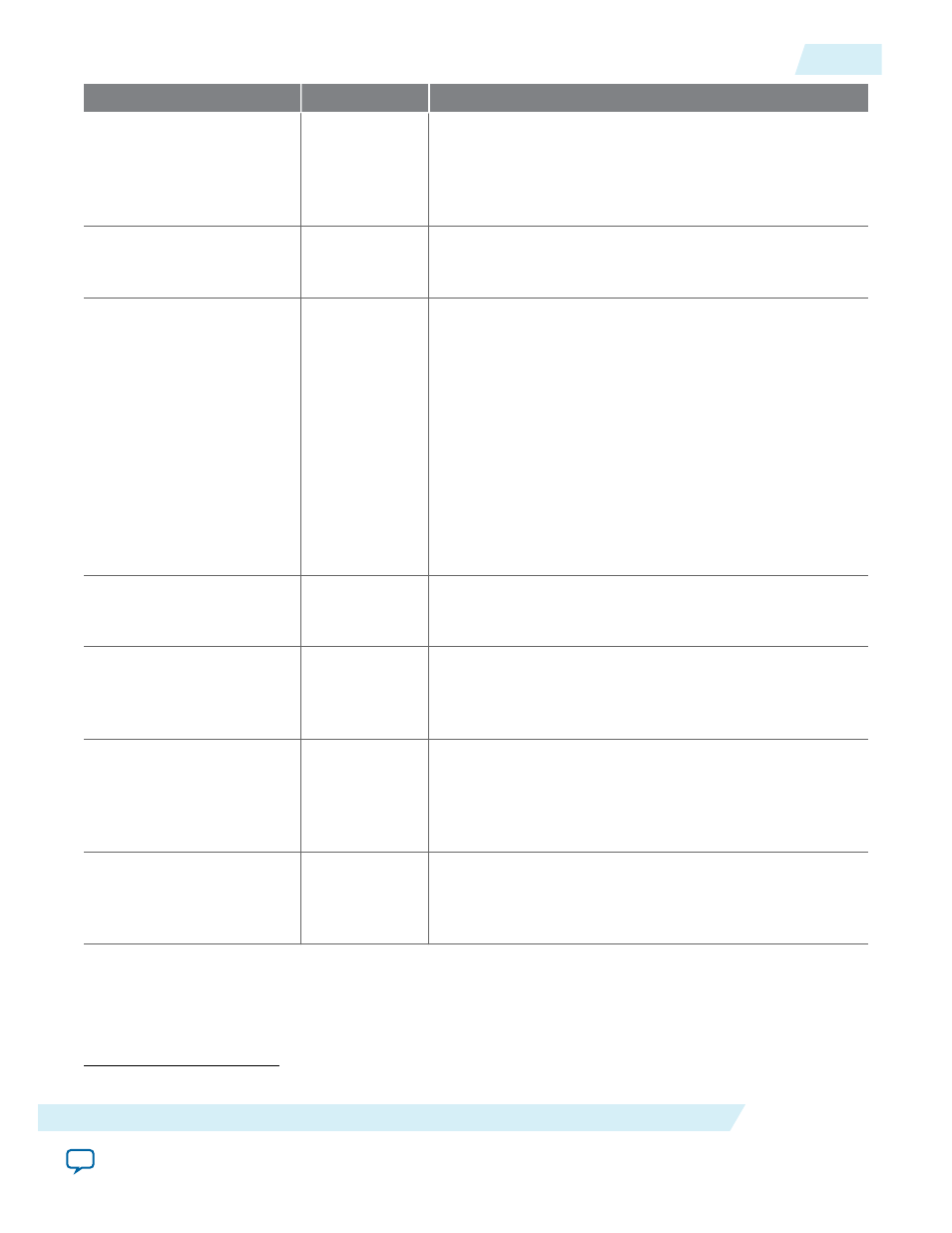

Parameter

HDL Parameter

Description

Usedw[]

lpm_widthu

Specifies the width of the

usedw

port for the FIFO IP core

in SCFIFO mode, or the width of the

rdusedw

and

wrusedw

ports for the FIFO IP core in DCFIFO mode. For

the FIFO IP core in DCFIFO_MIXED_WIDTHS mode, it

only represents the width of the

wrusedw

port.

How deep should the

FIFO be?

lpm_numwords

Specifies the depths of the FIFO you require. The value

must be at least 4. The value assigned must comply with

the 2

LPM_WIDTHU

equation.

Which kind of read

access do you want with

the rdreq signal?

lpm_showahead

Specifies whether the FIFO is in normal synchronous FIFO

mode or show-ahead mode synchronous FIFO mode.

Fornormal synchronous FIFO mode, the FIFO IP core

treats the

rdreq

port as a normal read request that only

performs read operation when the port is asserted. For

show-ahead mode synchronous FIFO mode, the FIFO IP

core treats the

rdreq

port as a read-acknowledge that

automatically outputs the first word of valid data in the

FIFO IP core (when the

empty

or

rdempty

port is low)

without asserting the

rdreq

signal. Asserting the

rdreq

signal causes the FIFO IP core to output the next data

word, if available. If you turn on this parameter, you may

reduce performance.

Do you want a common

clock for reading and

writing the FIFO?

lpm_type

Identifies the library of parameterized modules (LPM)

entity name. The values are SCFIFO and DCFIFO.

Disable overflow

checking. Writing to a

full FIFO will corrupt

contents

overflow_

checking

Specifies whether or not to enable the protection circuitry

for overflow checking that disables the

wrreq

port when

the FIFO IP core is full. This parameter is enabled by

default.

Disable underflow

checking. Reading from

an empty FIFO will

corrupt contents.

underflow_

checking

Specifies whether or not to enable the protection circuitry

for underflow checking that disables the

rdreq

port when

the FIFO IP core is empty. This parameter is enabled by

default. Note that reading from an empty SCFIFO mode

gives unpredictable results.

Add an extra MSB to

usedw

(2)

add_usedw_msb_

bit

Increases the width of the

rdusedw

and

wrusedw

ports by

one bit. By increasing the width, it prevents the FIFO IP

core from rolling over to zero when it is full. This

parameter is disabled by default.

(2)

Applicable in DCFIFO mode only.

UG-M10MEMORY

2015.05.04

FIFO IP Core Parameters for MAX 10 Devices

9-5

FIFO IP Core References

Altera Corporation