Altmemmult ip core parameters for max 10 devices – Altera MAX 10 Embedded Memory User Manual

Page 70

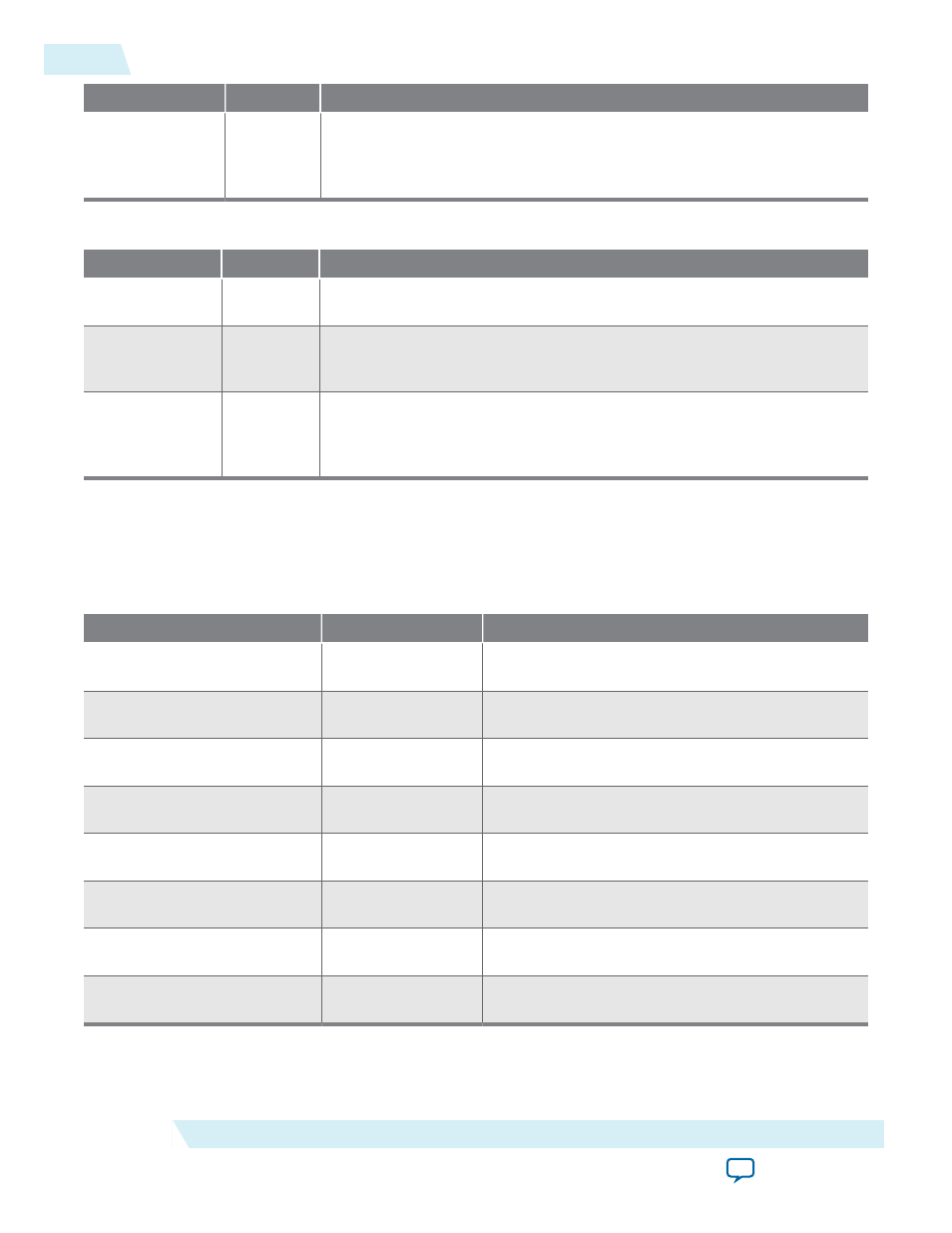

Signal

Required

Description

sload_data

No

Synchronous load data input port. Signal that specifies new multiplication

operation and cancels any existing multiplication operation. If the

MAX_

CLOCK_CYCLES_PER_RESULT

parameter has a value of

1

, the

sload_data

input port is ignored.

Table 10-2: ALTMEMMULT IP Core Output Signals

Signal

Required

Description

result[]

Yes

Multiplier output port. The size of the input port depends on the

WIDTH_R

parameter value.

result_valid

Yes

Indicates when the output is the valid result of a complete multiplication.

If the

MAX_CLOCK_CYCLES_PER_RESULT

parameter has a value of

1

, the

result_valid

output port is not used.

load_done

No

Indicates when the new coefficient has finished loading. The

load_don

e

signal asserts when a new coefficient has finished loading. Unless the

load_done

signal is high, no other coefficient value can be loaded into the

memory.

ALTMEMMULT IP Core Parameters for MAX 10 Devices

Table 10-3: ALTMEMMULT IP Core Parameters for MAX 10 Devices

This table lists the IP core parameters applicable to MAX 10 devices.

Option

Values

Description

How wide should the 'data_

in' input bus be?

2, 3, 4, 5, 6, 7, 8, 16,

24, and 32

Specifies the width of the

data_in

port.

What is the representation of

'data_in'?

SIGNED,

UNSIGNED

Specifies whether the

data_in

input port is signed

or unsigned.

How wide should the

coefficient be?

2, 3, 4, 5, 6, 7, 8, 16,

24

Specifies the width of the

coeff_in

port.

What is the representation of

the coefficient?

SIGNED,

UNSIGNED

Specifies whether the

coeff_in

input port and the

pre-loaded coefficients are signed or unsigned.

What is the value of the

initial coefficient?

0, 1, 2, 3, and 4

Specifies value of the first fixed coefficient.

Create ports to allow loading

coefficients

On/Off

Creates the

coeff_in

and

sload_coeff

port.

Create a synchronous clear

input

On/Off

Creates the

sclr

port.

What should the RAM block

type be?

Auto, M9K

Specifies the RAM block type.

10-2

ALTMEMMULT IP Core Parameters for MAX 10 Devices

UG-M10MEMORY

2015.05.04

Altera Corporation

ALTMEMMULT IP Core References