Rom: 1-port ip core signals for max 10 devices, Rom: 1-port ip core signals for max 10 devices -2 – Altera MAX 10 Embedded Memory User Manual

Page 47

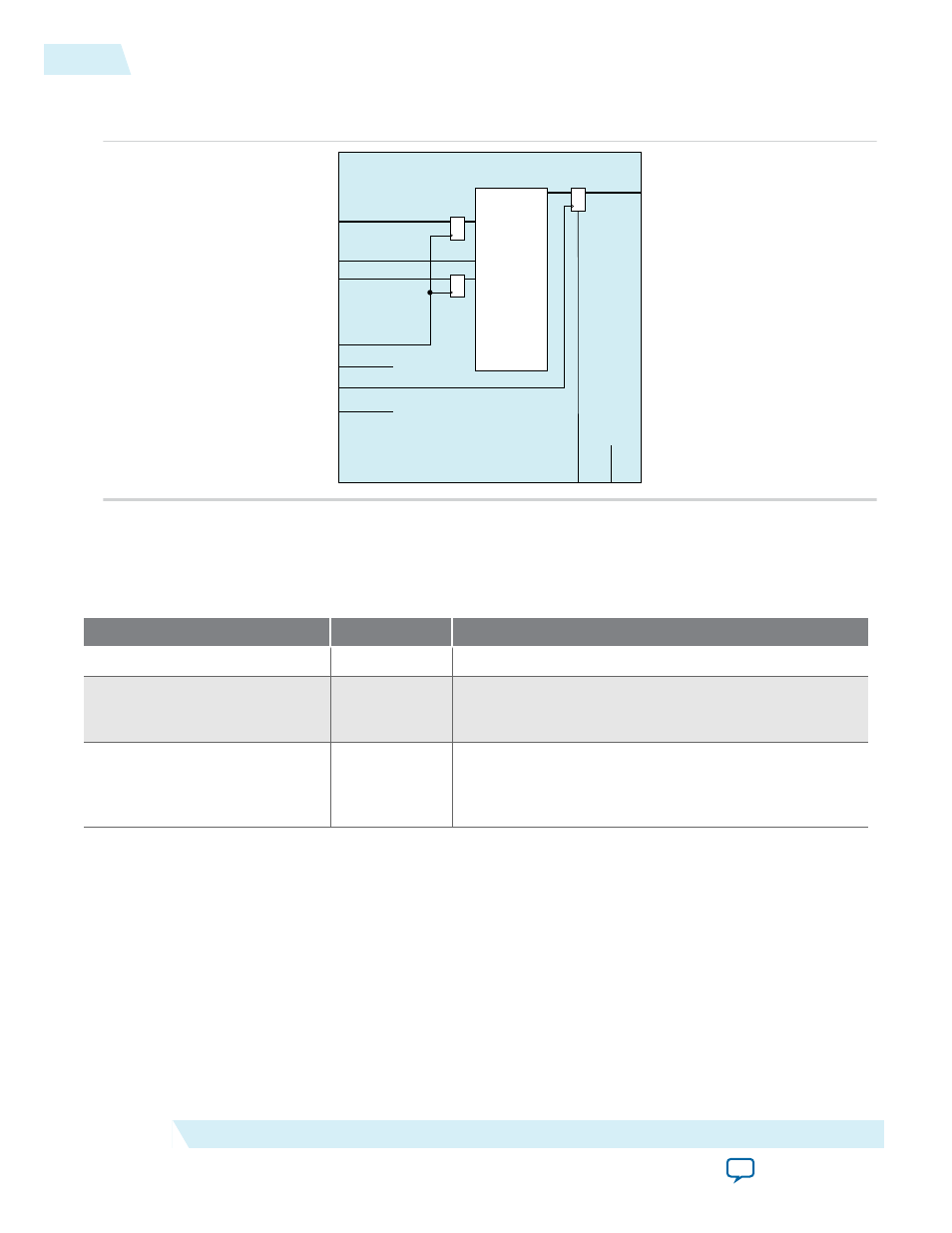

Figure 6-2: ROM: 1-PORT IP Core Signals with the Dual Clock: Use Separate 'Input' and 'Output' Clocks

Option Enabled

addressstall_a

outclock

outclocken

q[]

inaclr

address[]

rden

inclocken

inclock

outaclr

ROM: 1-PORT IP Core Signals For MAX 10 Devices

Table 6-1: ROM: 1-PORT IP Core Input Signals

Signal

Required

Description

address

Yes

Address input to the memory.

addressstall_a

Optional

Address clock enable input to hold the previous address

of

address_a

port for as long as the

addressstall_a

port is high.

rden

Optional

Read enable input for

rdaddress

port. The

rden

port is

supported when the

use_eab

parameter is set to

OFF

.

Instantiate the IP if you want to use read enable feature

with other memory blocks.

6-2

ROM: 1-PORT IP Core Signals For MAX 10 Devices

UG-M10MEMORY

2015.05.04

Altera Corporation

ROM: 1-PORT IP Core References