Altera MAX 10 Embedded Memory User Manual

Page 61

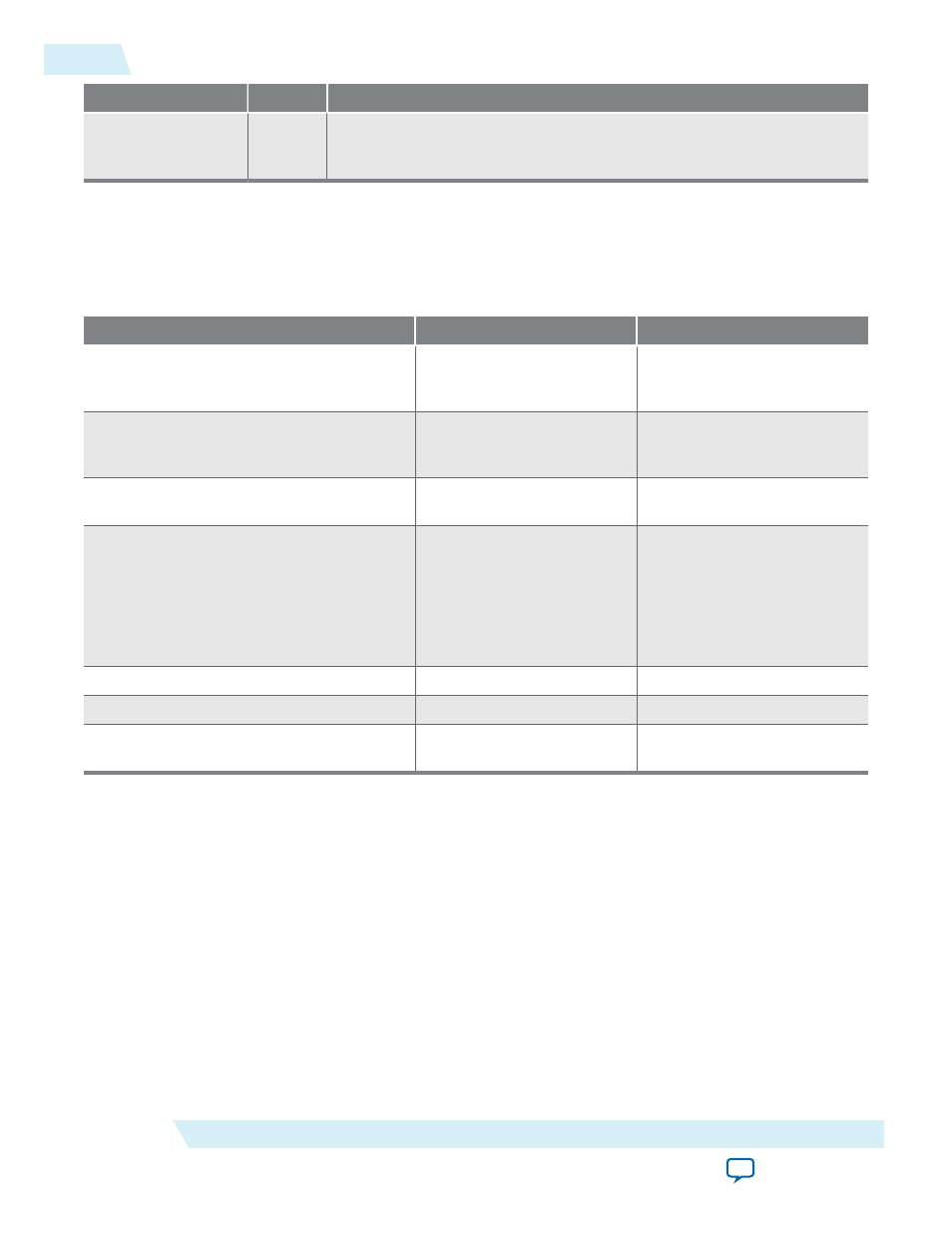

Signal

Required

Description

taps[]

Yes

Output from the regularly spaced taps along the shift register. Output

port

WIDTH * NUMBER_OF_TAPS

wide. This port is an aggregate of all the

regularly spaced taps (each

WIDTH

bits) along the shift register.

Shift Register (RAM-based) IP Core Parameters for MAX 10 Devices

Table 8-3: Shift Register (RAM-based) IP Core Parameters for MAX 10 Devices

This table lists the IP core parameters applicable to MAX 10 devices.

Option

Values

Description

How wide should the "shiftin" input and

the "shiftout" output buses be?

1, 2, 3, 4, 5, 6, 7, 8, 12, 16, 24,

32, 48, 64, 96, 128, 192, and

256.

Specifies the width of the

input pattern.

How many taps would you like?

1, 2, 3, 4, 5, 6, 7, 8, 12, 16, 24,

32, 48, 64, 96, and 128.

Specifies the number of

regularly spaced taps along

the shift register.

Create groups for each tap output

On/Off

Creates groups for each tap

output.

How wide should the distance between

taps be?

3, 4, 5, 6, 7, 8, 16, 32, 64, and

128

Specifies the distance

between the regularly spaced

taps in clock cycles. This

number translates to the

number of RAM words that

will be used. The value must

be at least 3.

Create a clock enable port

On/Off

Creates the

clken

port

Create an asynchronous clear port

On/Off

Creates the

aclr

port.

What should the RAM block type be?

Auto, M9K

Specifies the RAM block

type.

8-2

Shift Register (RAM-based) IP Core Parameters for MAX 10 Devices

UG-M10MEMORY

2015.05.04

Altera Corporation

Shift Register (RAM-based) IP Core References