Phy for pcie (pipe) input data from the phy mac, Phy for pcie (pipe) input data from the phy mac -7 – Altera Transceiver PHY IP Core User Manual

Page 195

For more information about _hw.tcl files, refer to refer to the Component Interface Tcl Reference chapter

in volume 1 of the Quartus II Handbook.

Related Information

PHY for PCIe (PIPE) Input Data from the PHY MAC

Input data signals are driven from the PHY MAC to the PCS. This interface is compliant to the

appropriate PIPE interface specification.

For more information about the Avalon-ST protocol, including timing diagrams, refer to the Avalon

Interface Specifications.

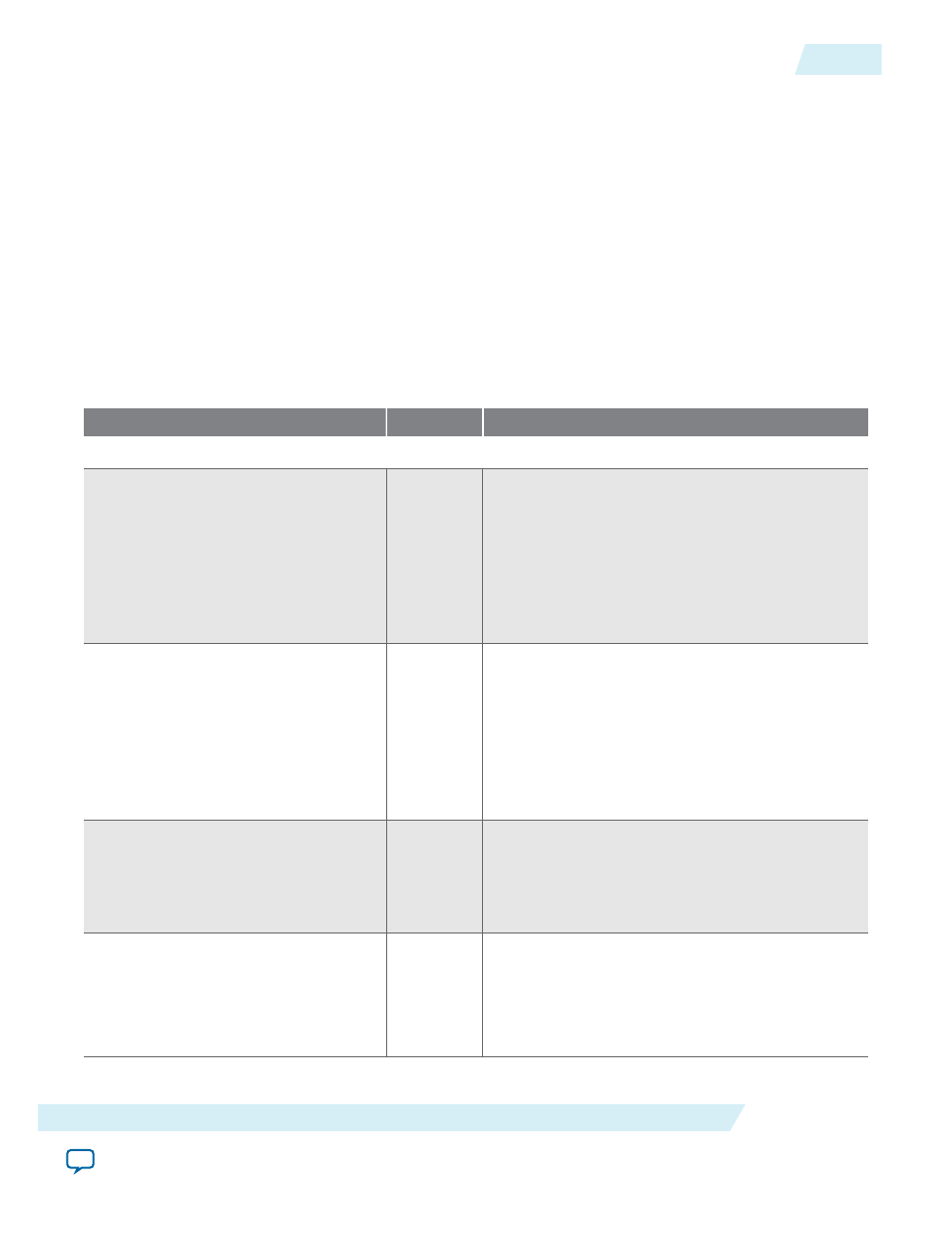

Table 8-3: Avalon-ST TX Inputs

Signal Name

Direction

Description

Gen1 and Gen2

pipe_txdata[31:0],[15:0]

, or

[7:0]

Input

Parallel PCI Express data input bus. For the 16-bit

interface, 16 bits represent 2 symbols of transmit

data. Bits [7:0] is transmitted first; bits[15:8] are

transmitted second. Bit 0 if the first to be

transmitted. For the 32-bit interface, 32 bits

represent the 4 symbols of TX data. Bits[23:16] are

the third symbol to be transmitted and bits [31:24]

are the fourth symbol.

pipe_txdatak[(3:0],[1:0]

or

[0]

Input

For Gen1 and Gen2, data and control indicator for

the received data. When 0, indicates that pipe_

txdata is data, when 1, indicates that

pipe_

txdata

is control.

For Gen3, Bit[0] corresponds to

pipe_

txdata[7:0]

, bit[1] corresponds to

pipe_

txdata[15:8]

, and so on.

pipe_txcompliance

Input

Asserted for one cycle to set the running disparity

to negative. Used when transmitting the

compliance pattern. Refer to section 6.11 of the

Intel PHY Interface for PCI Express (PIPE)

Architecture for more information.

pipe_tx_data_valid[<n>-1:0]

Input

For Gen3,

pipe_tx_data_valid[<n>-1:0]

is

deasserted by the MAC to instruct the PHY to

ignore

pipe_txdata

for one clock cycle. A value of

0 indicates the PHY should use the data. A value of

1 indicates the PHY should not use the data.

UG-01080

2015.01.19

PHY for PCIe (PIPE) Input Data from the PHY MAC

8-7

PHY IP Core for PCI Express (PIPE)

Altera Corporation