Altera Transceiver PHY IP Core User Manual

Page 690

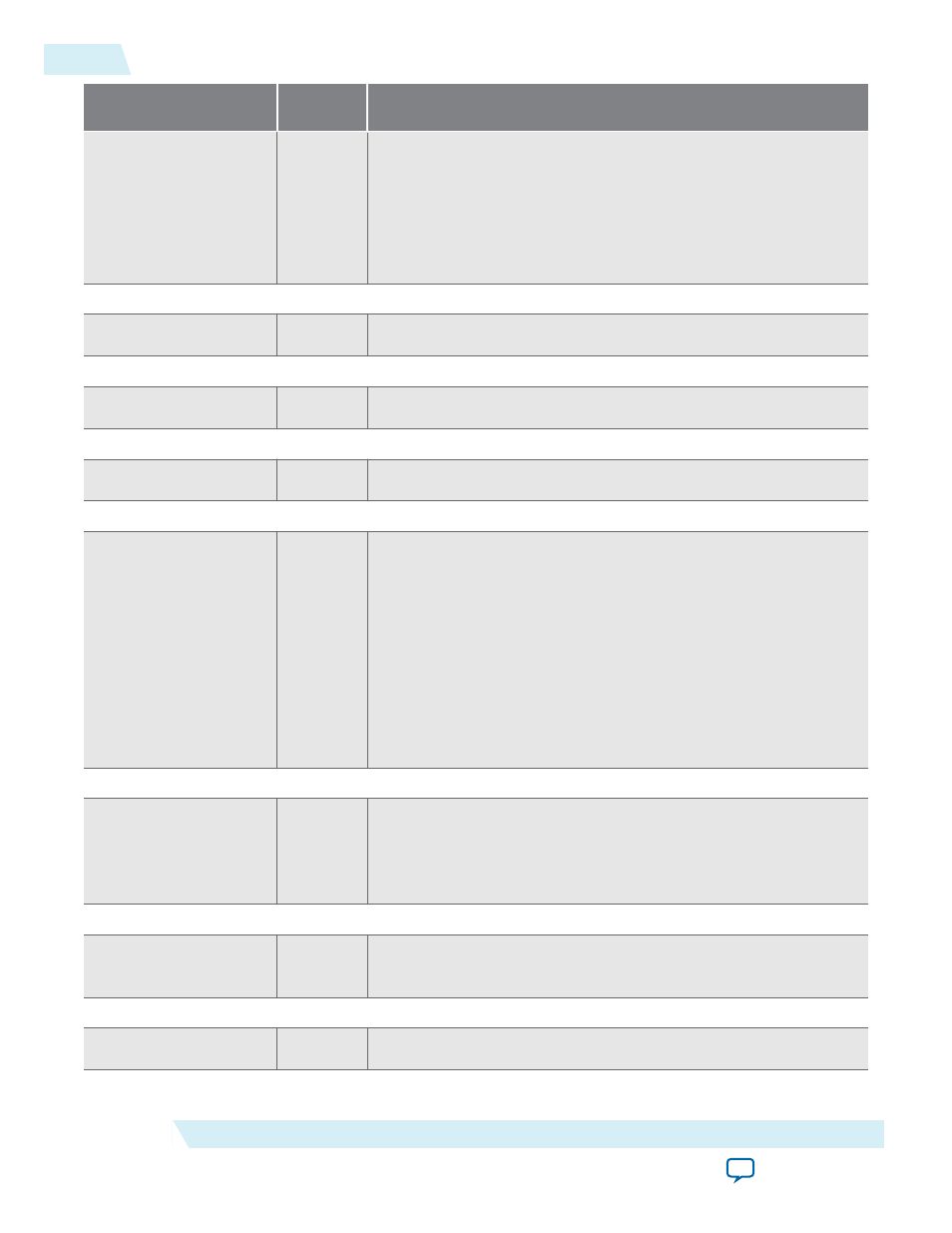

Date

Document

Version

Changes Made

June 2012

1.7

• DFE now automatically runs offset calibration and phase

interpolator (PI) phase calibration at power on.

• Added section explaining how to generate a reduced MIF file.

• Corrected definition of EyeQ control register. Writing a 1 to bit

0 enables the Eye monitor.

• Corrected bit-width typos in PMA Analog Registers.

Transceiver PHY Reset Controller

June 2012

1.7

• Initial release.

Custom

March 2012

1.6

• Added register definitions for address range 0x080–0x085.

Low Latency PHY

March 2012

1.6

• Removed register definitions for address range 0x080–0x085.

10GBASE-R

February 2012

1.5

• Added datapath latency numbers for Stratix V devices.

• Corrected bit range for

ERRORED_BLOCK_COUNT

.

• Added statement that the

cal_blk_powerdown

(0x021) and

pma_

tx_pll_is_locked

(0x022) registers are only available when the

Use external PMA control and reconfig option is turned On on

the Additional Options tab of the GUI.

• Clarified that the BER count functionality is for Stratix IV

devices only.

• Removed

pma_rx_signaldetect

register. The 10GBASE-R

PHY does not support this functionality.

XAUI

February 2012

1.5

• Removed reset bits at register 0x081. The reset implemented Cat

register 0x044 provides more comprehensive functionality.

• Removed

pma_rx_signaldetect

register. The XAUI PHY does

not support this functionality.

PCI Express (PIPE)

February 2012

1.5

• Updated definition of

fixedclk

. It can be derived from

pll_

ref_clk

.

Custom

February 2012

1.5

• Removed register definitions for Low Latency PHY.

21-30

Revision History for Previous Releases of the Transceiver PHY IP Core

UG-01080

2015.01.19

Altera Corporation

Additional Information for the Transceiver PHY IP Core