Offset cancellation, Duty cycle calibration, Offset cancellation -13 – Altera Transceiver PHY IP Core User Manual

Page 530: Duty cycle calibration -13

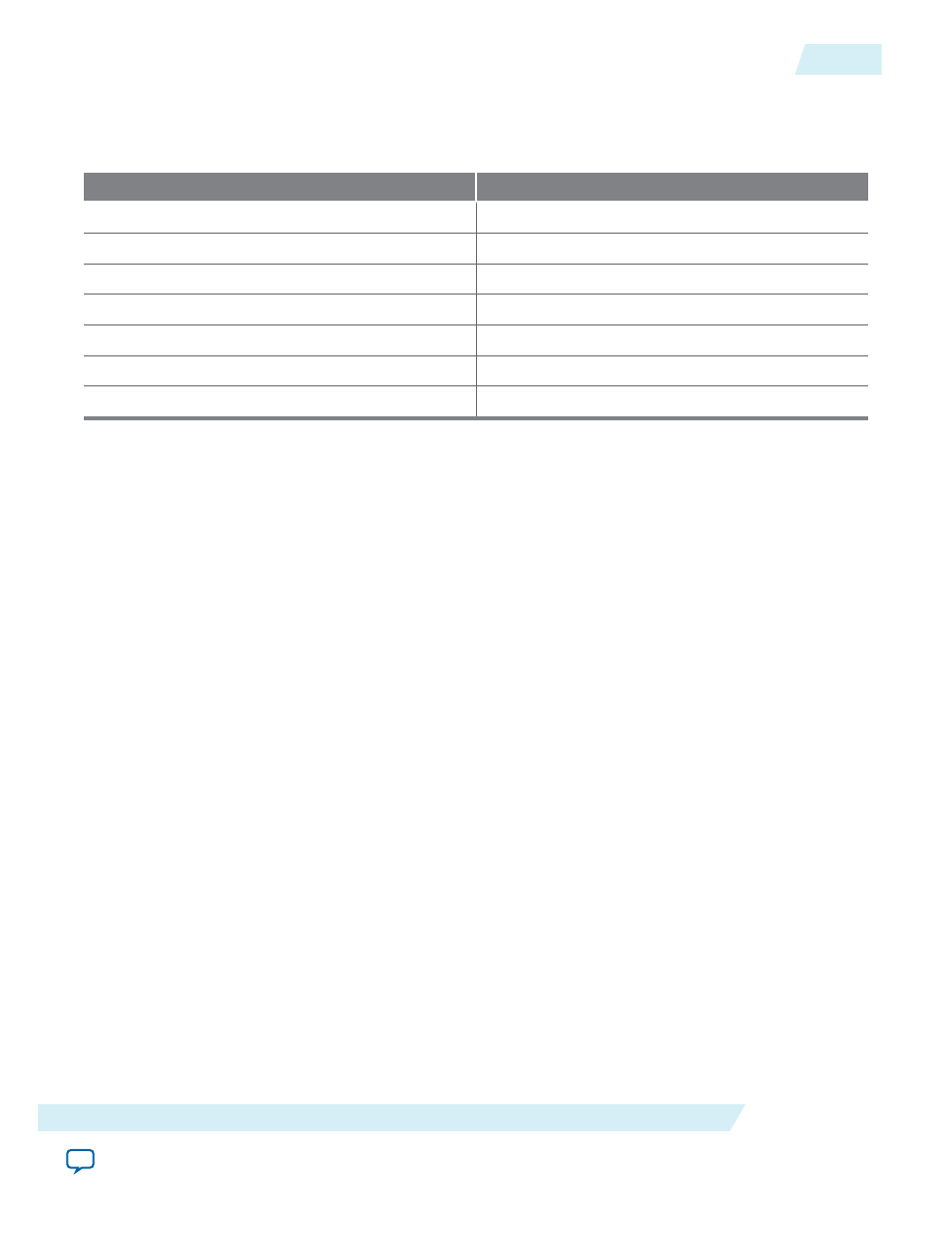

The following table lists the address range for the Transceiver Reconfiguration Controller and the reconfi‐

guration and signal integrity modules. The Avalon-MM interface uses byte addresses.

Table 16-8: Transceiver Reconfiguration Controller Address Map

Address

Link

7'h08-7'h0C

PMA Analog Control Registers

7'h10-7'h14

EyeQ Registers

7'h18-7'h1C

DFE Registers

7'h28-7'h2C

AEQ Registers

7'h30-7'h34

ATX PLL Calibration Registers

7'h38-7'h3C

Streamer Module Registers

7'h40-7'h44

PLL Reconfiguration

Transceiver Reconfiguration Controller Calibration Functions

The Transceiver Reconfiguration Controller supports various calibration functions to enhance the

performance and operation of any connected transceiver PHY IP core. Refer to Resource Utilization for

Stratix V Devices for the resource utilization of these calibration functions.

Offset Cancellation

The offset cancellation function adjusts the offsets within the RX PMA and the CDR parameters for

process variations to achieve optimal performance.

Offset cancellation runs only once upon power-up. The RX buffers are unavailable while this function is

running. This calibration feature is run automatically and enabled by default. Arria V and Cyclone V

devices do not require offset cancellation for the RX buffer.

Duty Cycle Calibration

The TX clocks generated by the CMU and travel across the clock network may introduce duty cycle

distortion (DCD). DCD calibration function reduces this distortion.

DCD runs once during device power up and you can manually trigger DCD after power up. Altera

recommends that you enable DCD for Arria V and Cyclone V devices if either of the following conditions

is true:

• The data rate is greater than or equal to 4.9152 Gbps

• The design dynamically reconfigures the TX PLL and the data rate is greater than or equal to 4.9152

Gbps

Related Information

UG-01080

2015.01.19

Transceiver Reconfiguration Controller Calibration Functions

16-13

Transceiver Reconfiguration Controller IP Core Overview

Altera Corporation