Tx pma parameters, Tx pma parameters -5 – Altera Transceiver PHY IP Core User Manual

Page 380

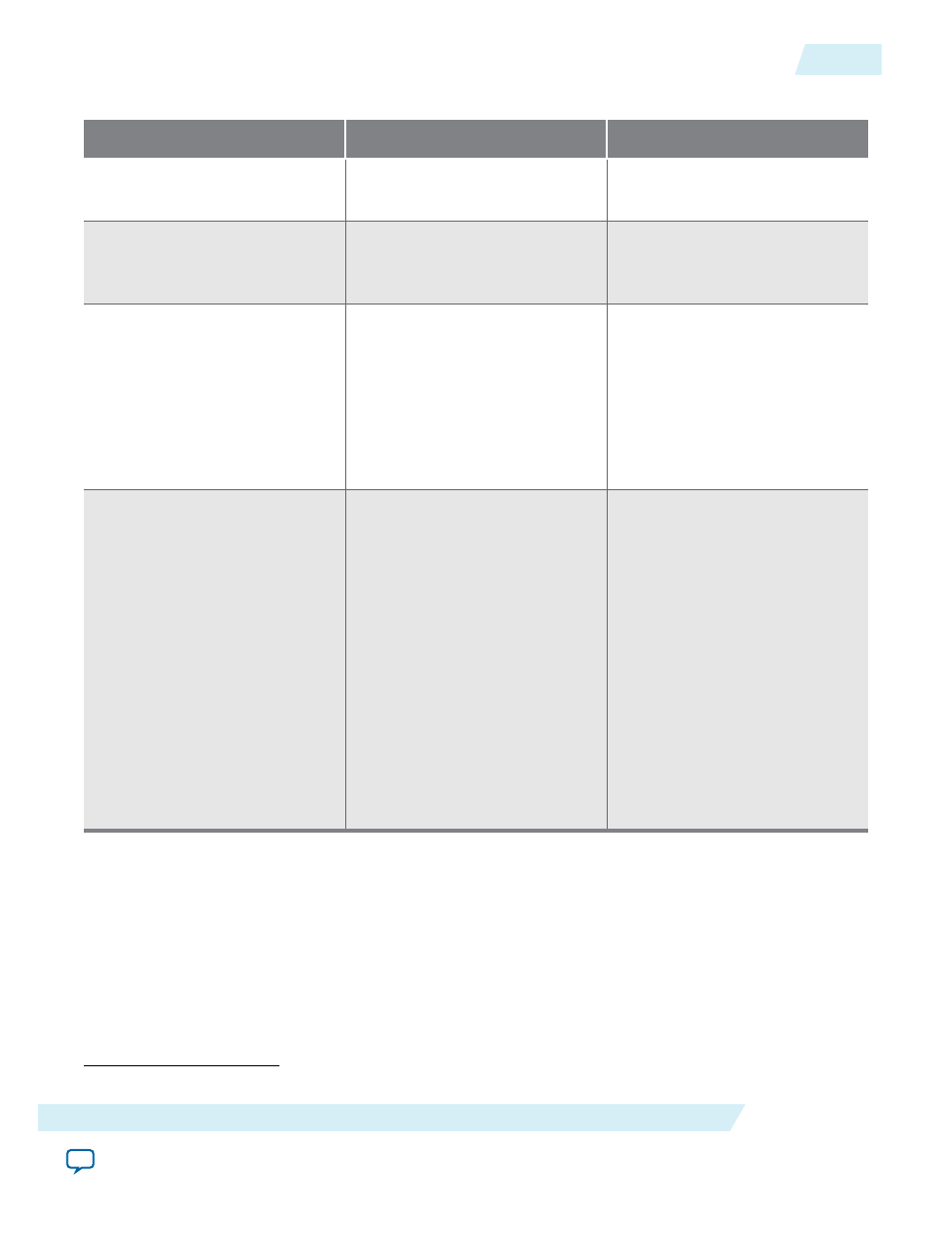

Table 13-3: PMA Options

Parameter

Range

Description

Data rate

Device Dependent

Specifies the data rate. The

maximum data rate is 12.5 Gbps.

PMA direct interface width

(12)

8.10,16,20,64,80

Specifies the PMA to FPGA

fabric interface width for PMA

Direct mode.

TX local clock division factor

1, 2, 4, 8

Specifies the value of the divider

available in the transceiver

channels to divide the input

clock to generate the correct

frequencies for the parallel and

serial clocks. This divisor divides

the fast clock from the PLL in

nonbonded configurations.

PLL base data rate

Device Dependent

Shows the base data rate of the

clock input to the TX PLL.The

PLL base data rate is computed

from the TX local clock division

factor multiplied by the data

rate.

Select a PLL base data rate that

minimizes the number of PLLs

required to generate all the

clocks for data transmission. By

selecting an appropriate PLL

base data rate, you can change

data rates by changing the TX

local clock division factor used

by the clock generation block.

Related Information

•

•

TX PMA Parameters

This section describes the TX PMA options you can specify.

Note: For more information about PLLs in Arria V devices, refer to the Arria V PLLs section in Clock

Networks and PLLs in Arria V Devices.

(12)

PMA Direct mode is supported for Arria V GT, ST, and GZ devices only.

UG-01080

2015.01.19

TX PMA Parameters

13-5

Arria V Transceiver Native PHY IP Core

Altera Corporation