Altera Transceiver PHY IP Core User Manual

Page 353

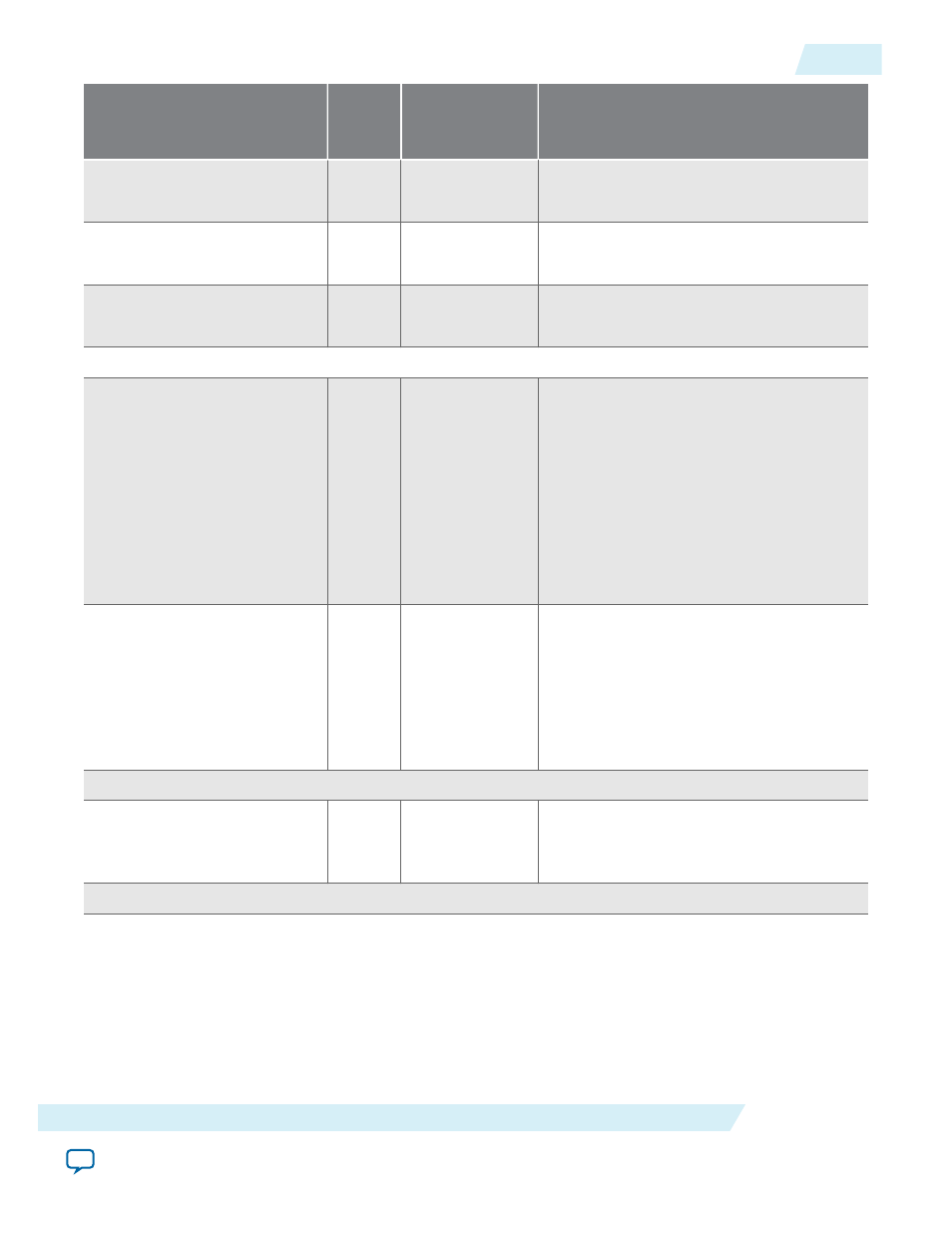

Name

Dir

Synchronous to

tx_std_coreclkin/

rx_std_coreclkin

Description

rx_std_pcfifo_empty[<n>-

1:0]

Output Yes

RX phase compensation FIFO status

empty flag.

tx_std_pcfifo_full[<n>-

1:0]

Output Yes

TX phase compensation FIFO status full

flag.

tx_std_pcfifo_empty[<n>-

1:0]

Output Yes

TX phase compensation FIFO status

empty flag.

Byte Ordering

rx_std_byteorder_ena[<n>-

1:0]

Input

No

Byte ordering enable. When this signal is

asserted, the byte ordering block initiates a

byte ordering operation if the Byte

ordering control mode is set to manual.

Once byte ordering has occurred, you

must deassert and reassert this signal to

perform another byte ordering operation.

This signal is an synchronous input signal;

however, it must be asserted for at least 1

cycle of

rx_std_clkout

.

rx_std_byteorder_flag[<n>

-1:0]

Output Yes

Byte ordering status flag. When asserted,

indicates that the byte ordering block has

performed a byte order operation. This

signal is asserted on the clock cycle in

which byte ordering occurred. This signal

is synchronous to the

rx_std_clkout

clock. You must a synchronizer this signal.

Byte Serializer and Deserializer

rx_std_byterev_ena[<n>-

1:0]

Input

No

This control signal is available in when the

PMA width is 16 or 20 bits. When asserted,

enables byte reversal on the RX interface.

8B/10B

UG-01080

2015.01.19

Standard PCS Interface Ports

12-55

Stratix V Transceiver Native PHY IP Core

Altera Corporation