Logical lane assignment restriction, Logical lane assignment restriction -25 – Altera Transceiver PHY IP Core User Manual

Page 213

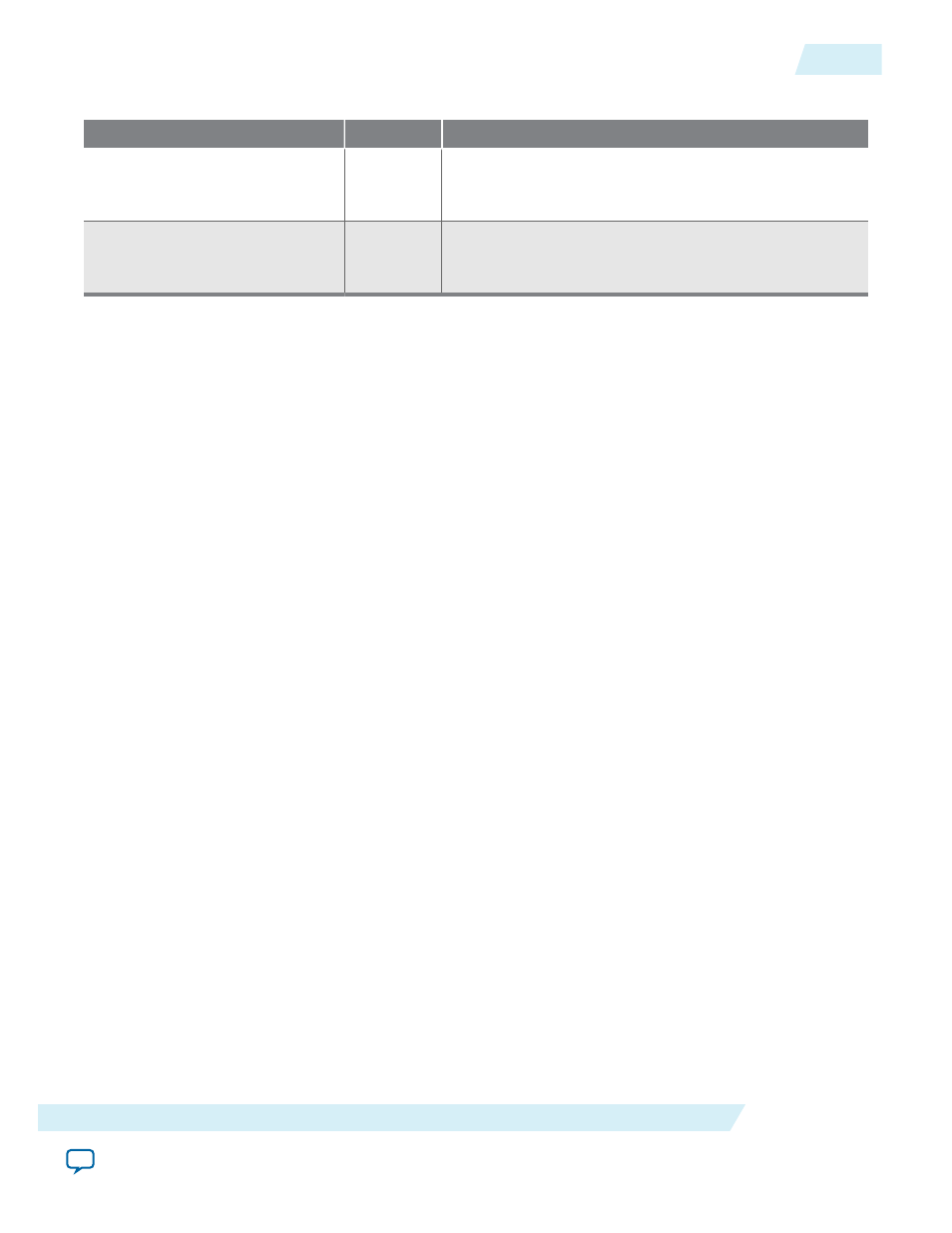

Table 8-12: Reconfiguration Interface Signals

Signal Name

Direction

Description

reconfig_to_xcvr [<r>70-

1:0]

Input

Reconfiguration signals from the Transceiver Reconfigu‐

ration Controller. <r> grows linearly with the number of

reconfiguration interfaces.

reconfig_from_xcvr [<r>46-

1:0]

Output

Reconfiguration signals to the Transceiver Reconfigura‐

tion Controller. <r> grows linearly with the number of

reconfiguration interfaces.

Logical Lane Assignment Restriction

If you are using ×6 or ×N bonding, transceiver dynamic reconfiguration requires that you assign the

starting channel number.

Transceiver dynamic reconfiguration requires that you assign the starting channel number. For PCIe ×8

configurations, logical channel 0 must be assigned to either physical transceiver channel 1 or channel 4 of

a transceiver bank. For PCIe x4 configurations, logical channel 1 must be assigned to either physical

transceiver channel 1 or channel 4 of a transceiver bank. However, if you have already created a PCB with

a different lane assignment for PCIe ×8 logical lane 0 or PCIe ×4 logical lane 1, you can use the

workaound shown in the example below to remove this restriction; the example redefines the

pma_bonding_master

parameter using the Quartus II Assignment Editor. In this example, the

pma_bonding_master

was originally assigned to physical channel 1. (The original assignment could also

have been to physical channel 4.) The to parameter reassigns the

pma_bonding_master

to the PHY IP

Core for PCI Express (PIPE) instance name. You must substitute the instance name from your design for

the instance name shown in quotation marks

Example 8-2: Overriding Logical Channel 0 Channel Assignment Restrictions in Stratix V

Devices for ×6 or ×N Bonding

set_parameter -name pma_bonding_master "\"1\"" -to "<PHY IP instance name>"

PHY for PCIe (PIPE) Simulation Files and Example Testbench

Refer to Running a Simulation Testbench for a description of the directories and files that the Quartus II

software creates automatically when you generate your PHY IP Core for PCI Express.

Refer to the Altera Wiki for an example testbench that you can use as a starting point in creating your

own verification environment.

Related Information

UG-01080

2015.01.19

Logical Lane Assignment Restriction

8-25

PHY IP Core for PCI Express (PIPE)

Altera Corporation