Sundance SMT702 User Manual

Page 38

Default

‘1’

‘1’

‘1’

‘1’

‘1’

‘1’

‘1’

‘1’

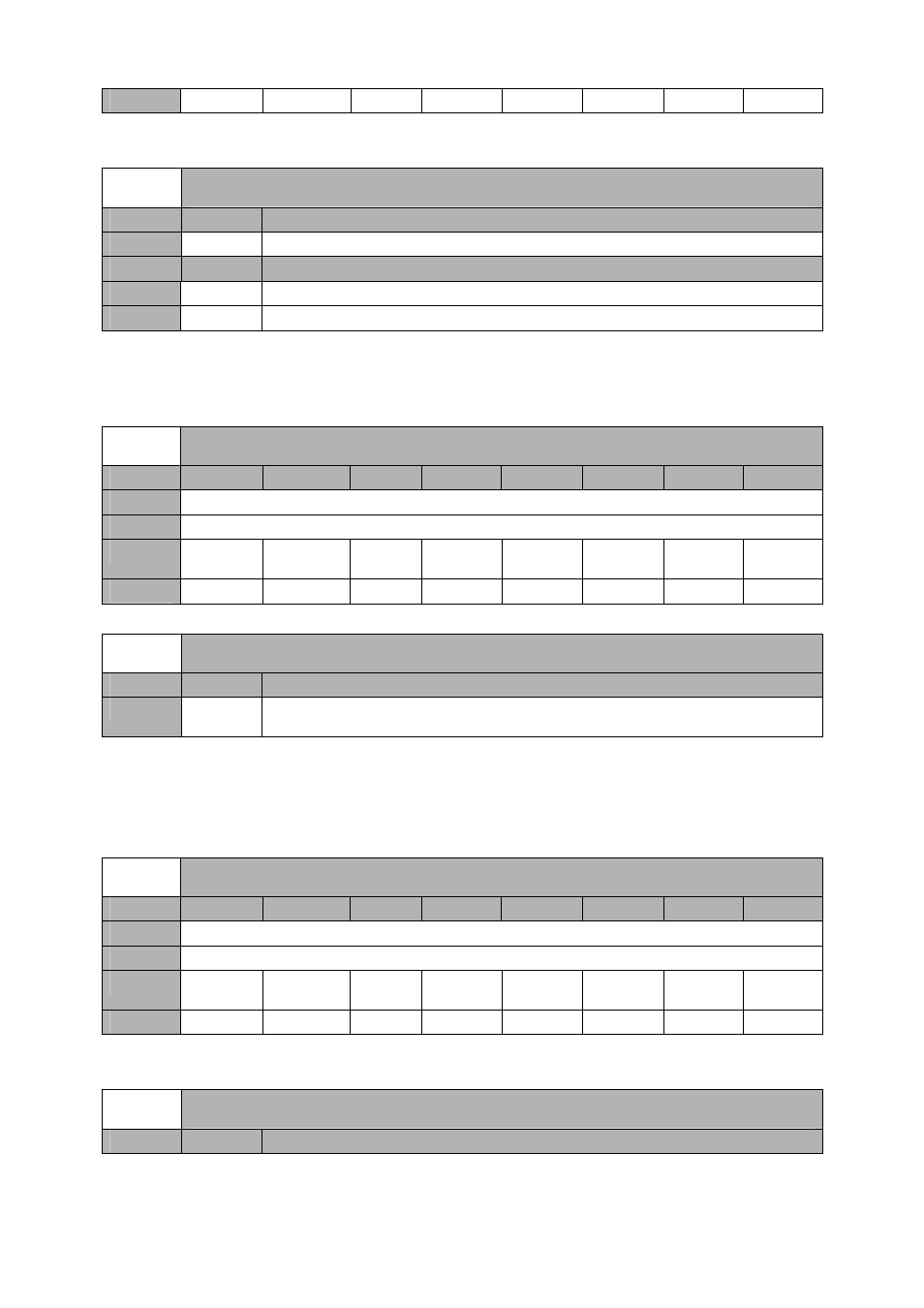

Offset 0x0400 -

ADCA (ADC083000) Register 0x2 – Offset Adjust – 0x48 (write and

read)

Setting

Bit 8-15

Description (Offset Adjust)

0

0

8-bit value - 0.176mV per bit – 0x0 is 0mv and 0xFF is 45mV.

Setting

Bit 7

Description (Offset sign)

0

0

Positive offset.

1

1

Negative offset.

4.3.1.2.8

ADCA (ADC083000) Register 0x3 – Full Scale Voltage

Adjust – 0x4C (write and read).

Offset 0x0400 -

ADCA (ADC083000) Register 0x3 – Full Scale Voltage Adjust – 0x4C (write and

read)

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

Adjust Value

Default

“10000000”

0

Adjust

Value

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Default

‘0’

‘1’

‘1’

‘1’

‘1’

‘1’

‘1’

‘1’

Offset 0x0400 -

ADCA (ADC083000) Register 0x3 – Full Scale Voltage Adjust – 0x4C

(write and read)

Setting

Bit 7-15

Description (Full Scale Voltage Adjust)

0

0

9-bit value – 20% adjustment around the nominal 700mVpp differential value – 0x0 is

560mVp-p and 0x1FF is 840mVp-p.

4.3.1.2.9

ADCA (ADC083000) Register 0xD – Extended Clock Phase

Adjust Fine – 0x74 (write and read).

Offset 0x0400 -

ADCA (ADC083000) Register 0xD – Extended Clock Phase Adjust Fine – 0x74

(write and read)

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

Phase Adjust (Fine)

Default

“00000000”

0

Phase

Adjust

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Default

‘0’

‘1’

‘1’

‘1’

‘1’

‘1’

‘1’

‘1’

Offset 0x0400 -

ADCA (ADC083000) Register 0xD – Extended Clock Phase Adjust Fine –

0x74 (write and read)

Setting

Bit 7-15

Description (Fine Adjust Magnitude)