Source link voltage and pre-emphasis controls, Dptx_pre_volt0, Source link voltage and pre-emphasis controls -9 – Altera DisplayPort MegaCore Function User Manual

Page 130: Dptx_pre_volt0 -9

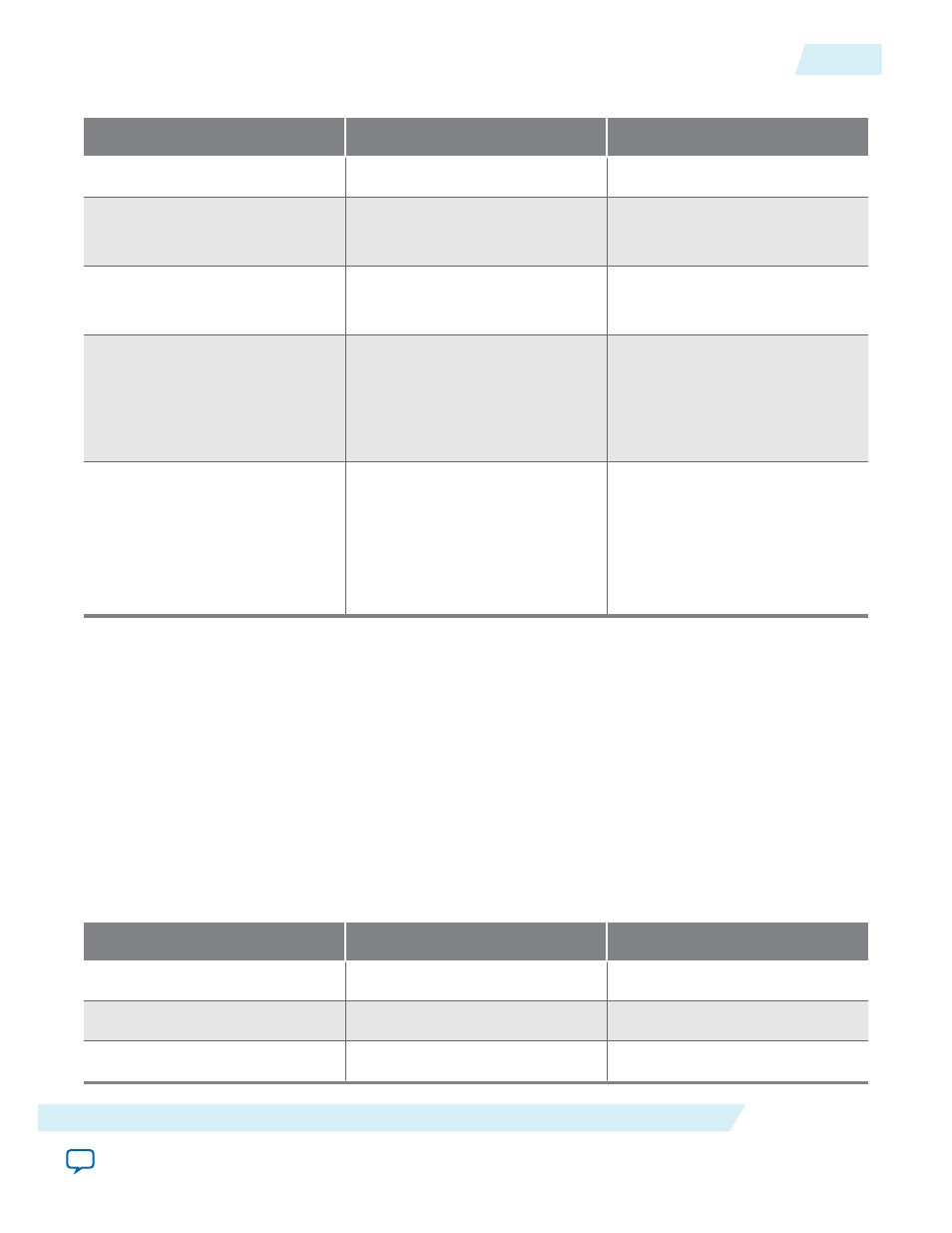

Table 9-18: DPTX0_MSA_MISC1 Bits

Bit

Bit Name

Function

31:7

Unused

6

COLORIMETRY

0 = ITU-R BT601-5

1 = ITU-R BT709-5

5

DYNAMIC_RANGE

0 = VESA (from 0 to maximum)

1 = CEA range

4:3

COMPONENT_FORMAT

00 = RGB

01 = YCbCr 4:2:2

10 = YCbCr 4:4:4

11 = Reserved

2:0

BPP

Bits per pixel format

• 000 = 6 bpc

• 001 = 8 bpc

• 010 = 10 bpc

• 011 = 12 bpc

• 100 = 16 bpc

Source Link Voltage and Pre-Emphasis Controls

This section describes the registers for the link voltage and pre-emphasis controls.

DPTX_PRE_VOLT0

These ports drive the respective

tx_analog_reconfig

ports.

Address: 0×0010

Direction: RW

Reset: 0×00000000

Table 9-19: DPTX_PRE_VOLT0 Bits

Bit

Bit Name

Function

31:4

Unused

3:2

PRE0

Pre-emphasis output on lane 0

1:0

VOLT0

Voltage swing output on lane 0

UG-01131

2015.05.04

Source Link Voltage and Pre-Emphasis Controls

9-9

DisplayPort Source Register Map and DPCD Locations

Altera Corporation