Altera DisplayPort MegaCore Function User Manual

Page 74

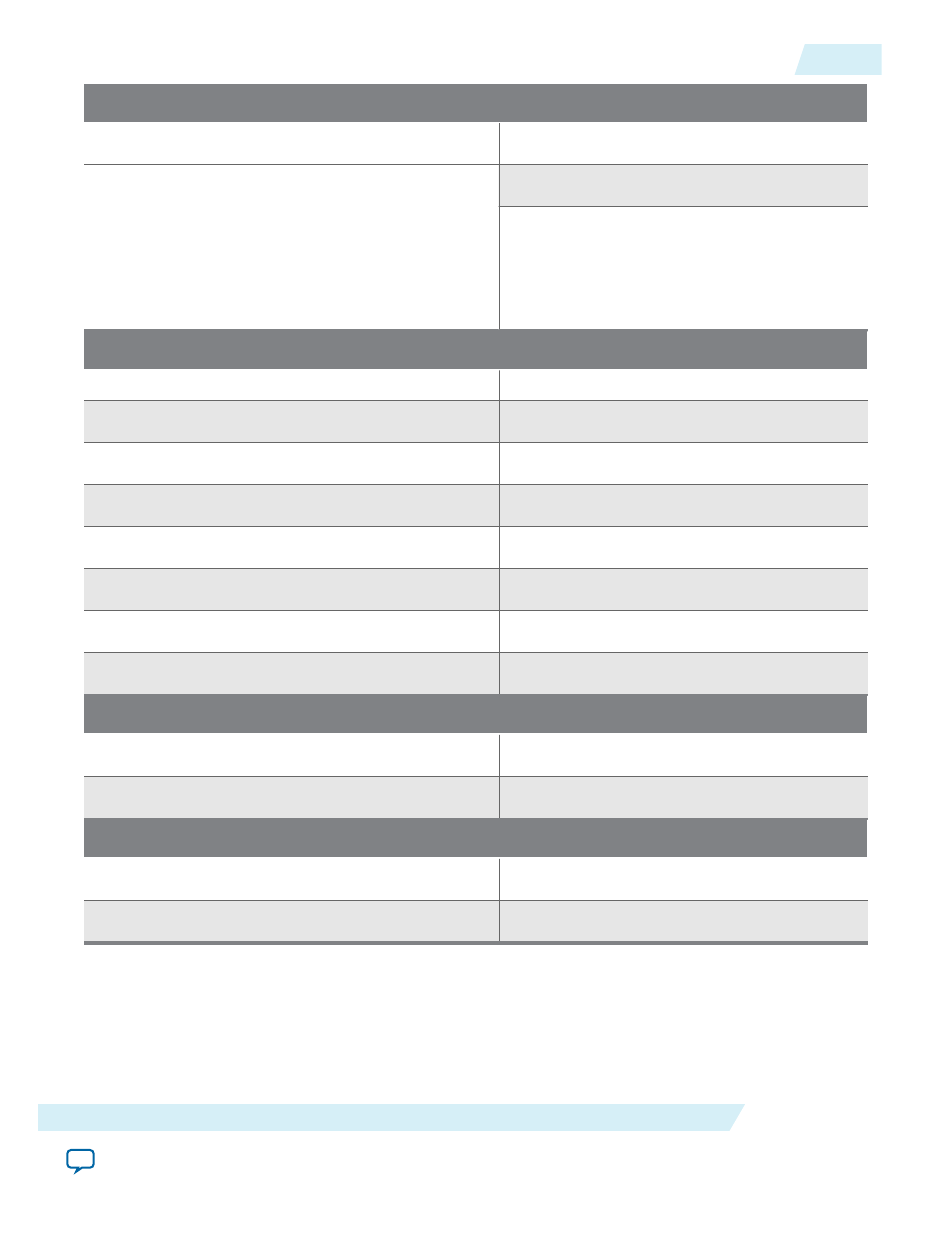

TX PLL0

Selected reference clock source

0

Selected clock network

×1 or ×N

Note: If you select ×1, you must instantiate

the PHY instance multiple times for

all data channels as per maximum

lane count parameter. This value is

for non-bonded mode.

RX PMA

Enable CDR dynamic reconfiguration

On

Number of CDR reference clocks

1

Selected CDR reference clock

0

Selected CDR reference clock frequency

135 MHz

PPM detector threshold

1000 ppm

Enable rx_is_lockedtodata port

On

Enable rx_is_lockedtoref port

On

Enable rx_set_locktodata and rx_set_locktoref ports

On

Standard PCS

Standard PCS protocol mode

Basic

Standard PCS/PMA interface width

20 (when symbol output mode is dual)

Byte Serializer and Deserializer

Enable TX byte serializer

Off (when symbol output mode is dual)

Enable RX byte deserializer

Off (when symbol output mode is dual)

Note: Currently, only Arria V GX, Arria V GZ, and Stratix V devices support 5.4 Gbps operation.

UG-01131

2015.05.04

Transceiver and Clocking

6-13

DisplayPort IP Core Hardware Demonstration

Altera Corporation