Altera DisplayPort MegaCore Function User Manual

Page 41

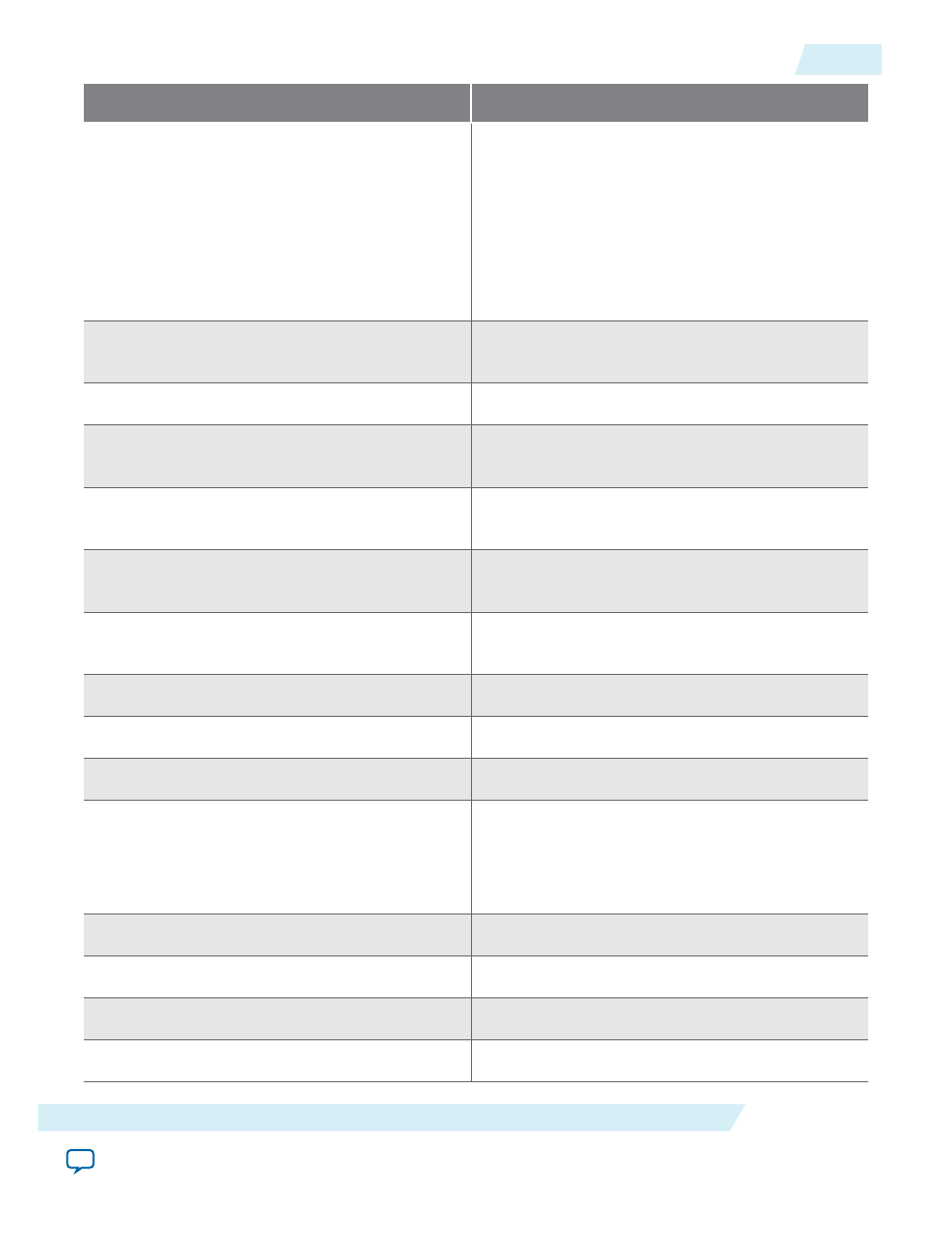

Parameter

Description

Pixel output mode

Select the number of pixels per clock (single, dual, or

quad symbol).

• If you select dual pixels per clock, the pixel clock

is ½ of the full rate clock and the video port

becomes two times wider.

• If you select four pixels per clock, the pixel clock

is ¼ of the full rate clock and the video port

becomes four times wider.

Sink scrambler seed value

Specify the initial seed value for the scrambler block.

Use 16’hFFFF for DP and 16’hFFFFE for eDP.

Invert transceiver polarity

Turn on to invert the transceiver polarity.

Export MSA

Turn on to enable the sink to export the MSA

interface to the top-level port interface.

IEEE OUI

Specify an IEEE organizationally unique identifier

(OUI) as part of the DPCD registers.

Enable GPU control

Turn on to use an embedded controller to control

the sink.

Enable AUX debug stream

Turn on to enable AUX traffic output to an

Avalon-ST port.

Support CTS test automation

Turn on to support automated test features.

Support secondary data channel

Turn on to enable secondary data.

Support audio data channel

Turn on to enable audio packet decoding.

Number of audio data channels

Specify the number of audio channels supported.

Note: To use this parameter, you must turn on

the Support secondary data channel

parameter.

6-bpc RGB or YCbCr 4:4:4 (18 bpp)

Turn on to support 18 bpp decoding.

8-bpc RGB or YCbCr 4:4:4 (24 bpp)

Turn on to support 24 bpp decoding.

10-bpc RGB or YCbCr 4:4:4 (30 bpp)

Turn on to support 30 bpp decoding.

12-bpc RGB or YCbCr 4:4:4 (36 bpp)

Turn on to support 36 bpp decoding.

UG-01131

2015.05.04

Sink Parameters

5-5

DisplayPort Sink

Altera Corporation