Altera DisplayPort MegaCore Function User Manual

Page 9

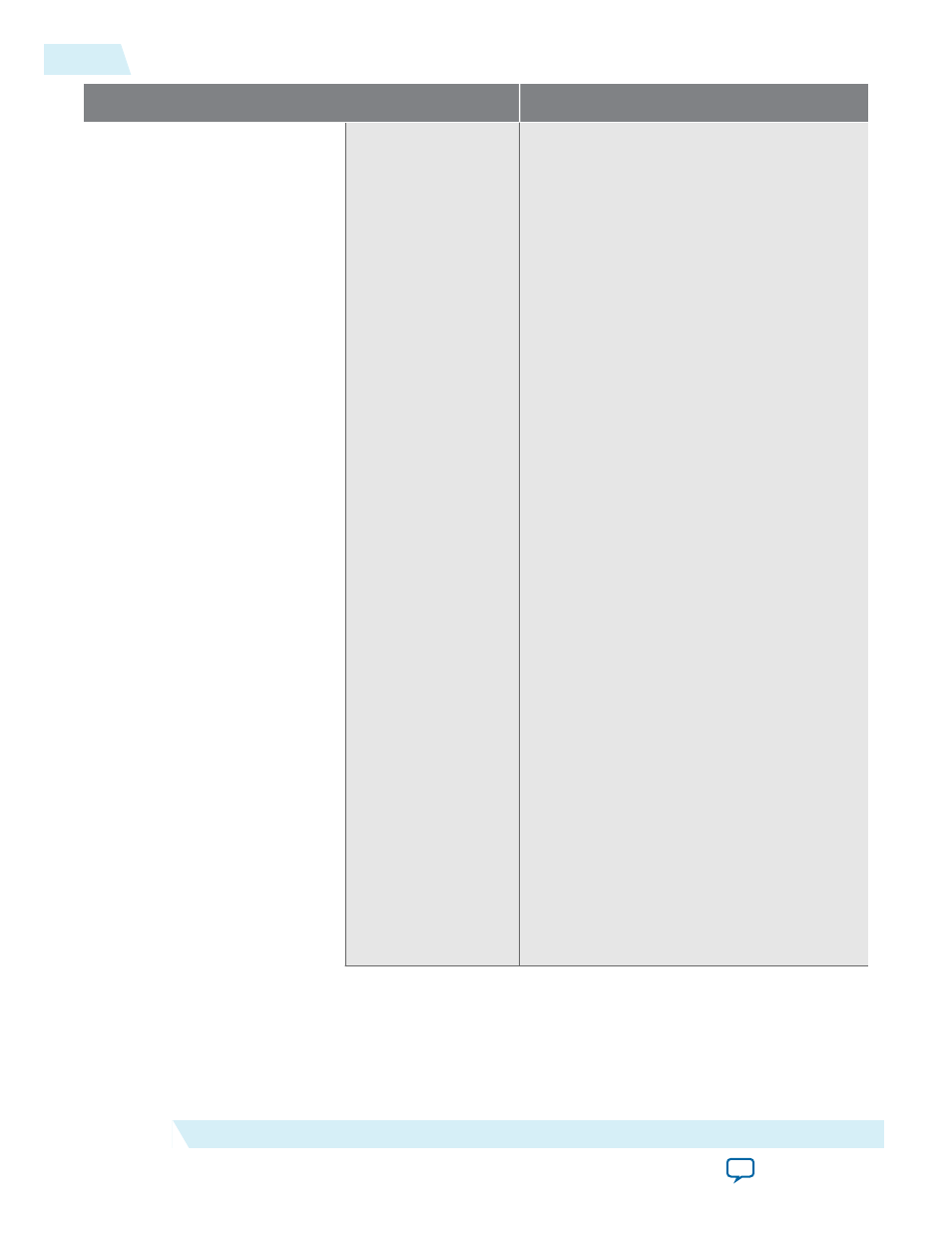

Item

Description

IP Core Information

Core Features

• Conforms to the Video Electronics

Standards Association (VESA) specifica‐

tion version 1.2a

• Scalable main data link

• 1, 2, or 4 lane operation

• 1.62, 2.7, and 5.4 gigabits per second

(Gbps) per lane with an embedded

clock

• Color support

• RGB 18, 24, 30, 36, or 48 bits per pixel

(bpp) color depths

• YCbCr 4:4:4 24, 30, 36, or 48 bpp color

depths

• YCbCr 4:2:2 16, 20, 24, or 32 bpp color

depths

• 40-bit (quad symbol) and 20-bit (dual

symbol) transceiver data interface

• Support for 1, 2, or 4 parallel pixels per

clock

• Multi-stream support (MST)

• 4Kp60 resolution support

• Source

• Embedded controller AUX channel

operation

• Accepts standard H-sync/V-sync/data

enable RGB and YCbCr input video

formats

• Supports audio and video streams

• Sink

• Finite state machine (FSM) or

embedded controller AUX channel

operation

• Produces a proprietary video output

• Auxiliary channel for 2-way communica‐

tion (link and device management)

• Hot plug detect (HPD)

• Sink announces its presence

• Sink requests the source’s attention

• AC coupling and low EMI

1-2

DisplayPort IP Core Quick Reference

UG-01131

2015.05.04

Altera Corporation

DisplayPort IP Core Quick Reference