Altera DisplayPort MegaCore Function User Manual

Page 39

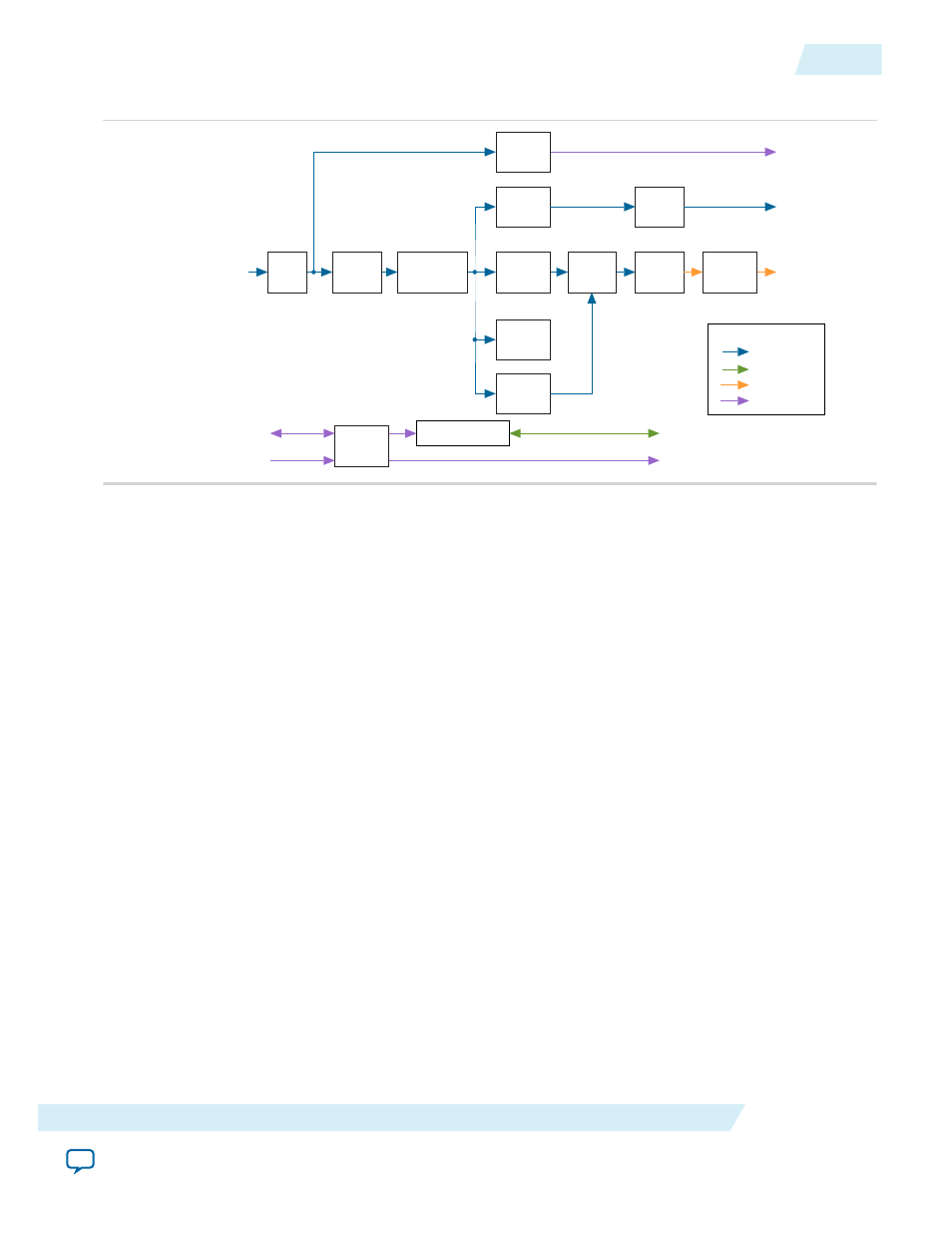

Figure 5-3: DisplayPort Sink Functional Block Diagram

Video Output

(rxN_video_out)

20-Bit (Dual Symbol)

or 40-Bit (Quad Symbol)

Data from Transceiver

(rx_xcvr_interface)

Bidirectional AUX Data (rx_aux)

AUX Debug Stream (rx_aux_debug)

Avalon-MM (rx_mgmt)

AUX

Controller

HPD

Controller Registers

De-Scrambler

DP2ST

Gearbox

SS

Decoder

IRQ

Control

VB-ID

Decoder

MSA

Decoder

8B/10B

Aligner

DCFIFO

DCFIFO

Steering

Secondary

Stream (rxN_ss)

HPD

rx_ss_clk

clk

rxN_vid_clk

aux_clk

Legend

Deskew

The device transceiver sends 20-bit (dual symbol) or 40-bit (quad symbol) parallel DisplayPort data to the

sink. Each data lane is clocked in to the IP core by its own respective clock output from the transceiver.

Inside the sink, the four independent clock domains are synchronized to the lane 0 clock. Then, the IP

core performs the following actions:

1. The IP core aligns the data stream and performs 8B/10B decoding.

2. The IP core deskews the data and then descrambles it.

3. The IP core splits the unscrambled data stream into parallel paths.

a. The SS decoder block performs secondary stream decoding, which the core transfers into the

rx_ss_clk

domain through a DCFIFO.

b. The main data path extracts all pixel data from the incoming stream. Then, the gearbox block

resamples the pixel data into the current bit-per-pixel data width. Next, the IP core crosses the pixel

data into the

rxN_vid_clk

domain through a DCFIFO. Finally, the IP core steers the data into a

single, dual, or quad pixel data stream.

c. MSA decode path.

d. Video decode path.

You configure the sink to output the video data as a proprietary data stream. You specify the output pixel

data width at 6, 8, 10, 12, or 16 bpc. This format can interface with downstream Altera Video and Image

Processing (VIP) Suite components.

The AUX controller can operate in an autonomous mode in which the sink controls all AUX channel

activity without an external embedded controller. The IP core outputs an AUX debugging stream so that

you can inspect the activity on the AUX channel in real time.

UG-01131

2015.05.04

Sink Functional Description

5-3

DisplayPort Sink

Altera Corporation