Dptx_mst_vcptab2, Dptx_mst_vcptab2 -16 – Altera DisplayPort MegaCore Function User Manual

Page 137

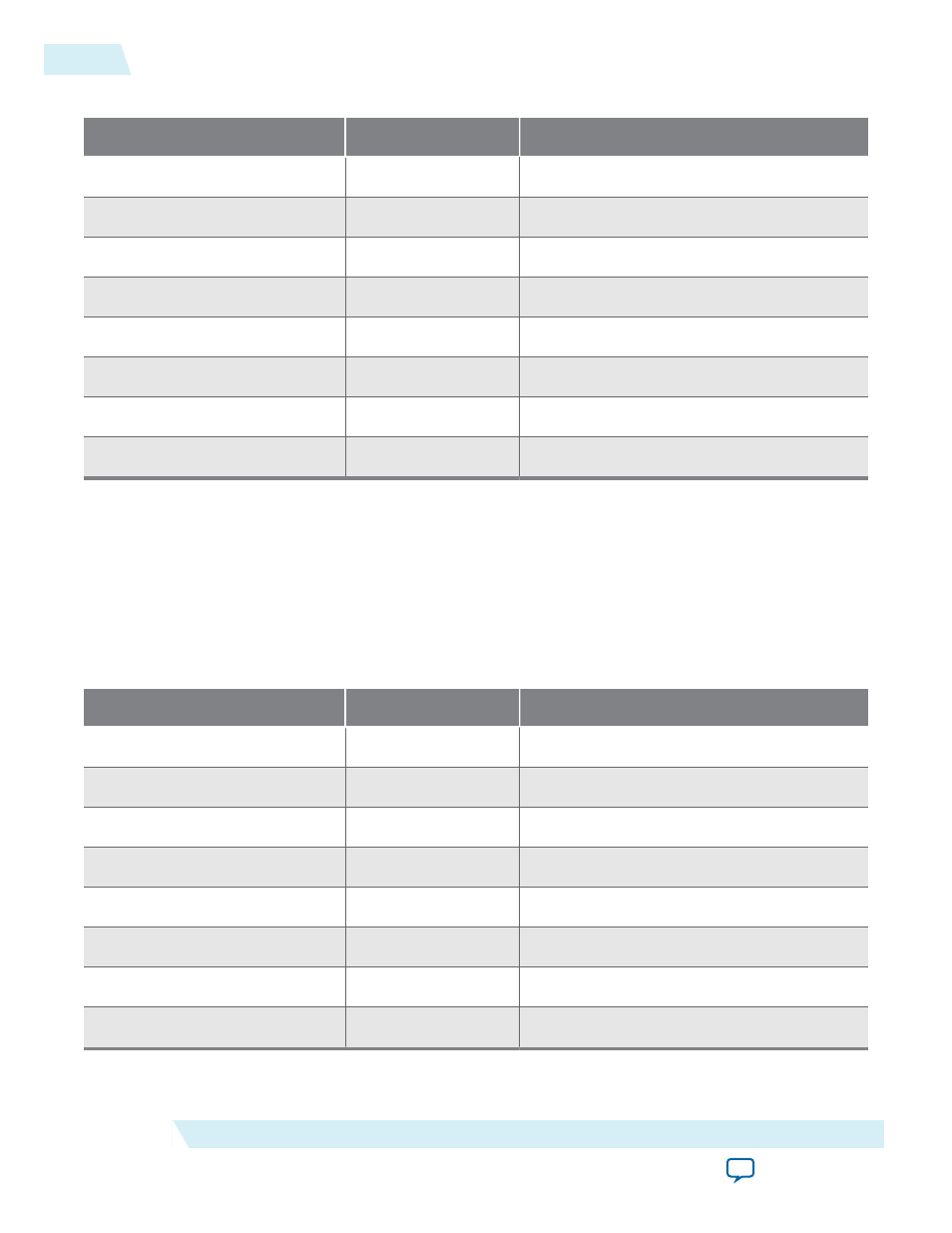

Table 9-31: DPTX_MST_VCPTAB1 Bits

Bit

Bit Name

Function

31:28

VCPSLOT15

VC payload ID or slot 15

27:24

VCPSLOT14

VC payload ID or slot 14

23:20

VCPSLOT13

VC payload ID or slot 13

19:16

VCPSLOT12

VC payload ID or slot 12

15:12

VCPSLOT11

VC payload ID or slot 11

11:8

VCPSLOT10

VC payload ID or slot 10

7:4

VCPSLOT9

VC payload ID or slot 9

3:0

VCPSLOT8

VC payload ID or slot 8

DPTX_MST_VCPTAB2

VC Payload ID Table

Address: 0×00a4

Direction: RW

Reset: 0×00000000

Table 9-32: DPTX_MST_VCPTAB2 Bits

Bit

Bit Name

Function

31:28

VCPSLOT23

VC payload ID or slot 23

27:24

VCPSLOT22

VC payload ID or slot 22

23:20

VCPSLOT21

VC payload ID or slot 21

19:16

VCPSLOT20

VC payload ID or slot 20

15:12

VCPSLOT19

VC payload ID or slot 19

11:8

VCPSLOT18

VC payload ID or slot 18

7:4

VCPSLOT17

VC payload ID or slot 17

3:0

VCPSLOT16

VC payload ID or slot 16

9-16

DPTX_MST_VCPTAB2

UG-01131

2015.05.04

Altera Corporation

DisplayPort Source Register Map and DPCD Locations