Clocked video input interface – Altera DisplayPort MegaCore Function User Manual

Page 54

Clocked Video Input Interface

The

rxN_video_out

interface may interface with a clocked video input (CVI). CVI accepts the following

video signals with a separate synchronization mode:

datavalid

,

de

,

h_sync

,

v_sync

,

f

,

locked

, and

data

.

The DisplayPort

rxN_video_out

interface has the following signals:

rxN_vid_valid

,

rxN_vid_sol

,

rxN_vid_eol

,

rxN_vid_sof

,

rxN_vid_eof

,

rxN_vid_locked

, and

rxN_vid_data

.

The following table describes how to connect the CVI and DisplayPort sink signals.

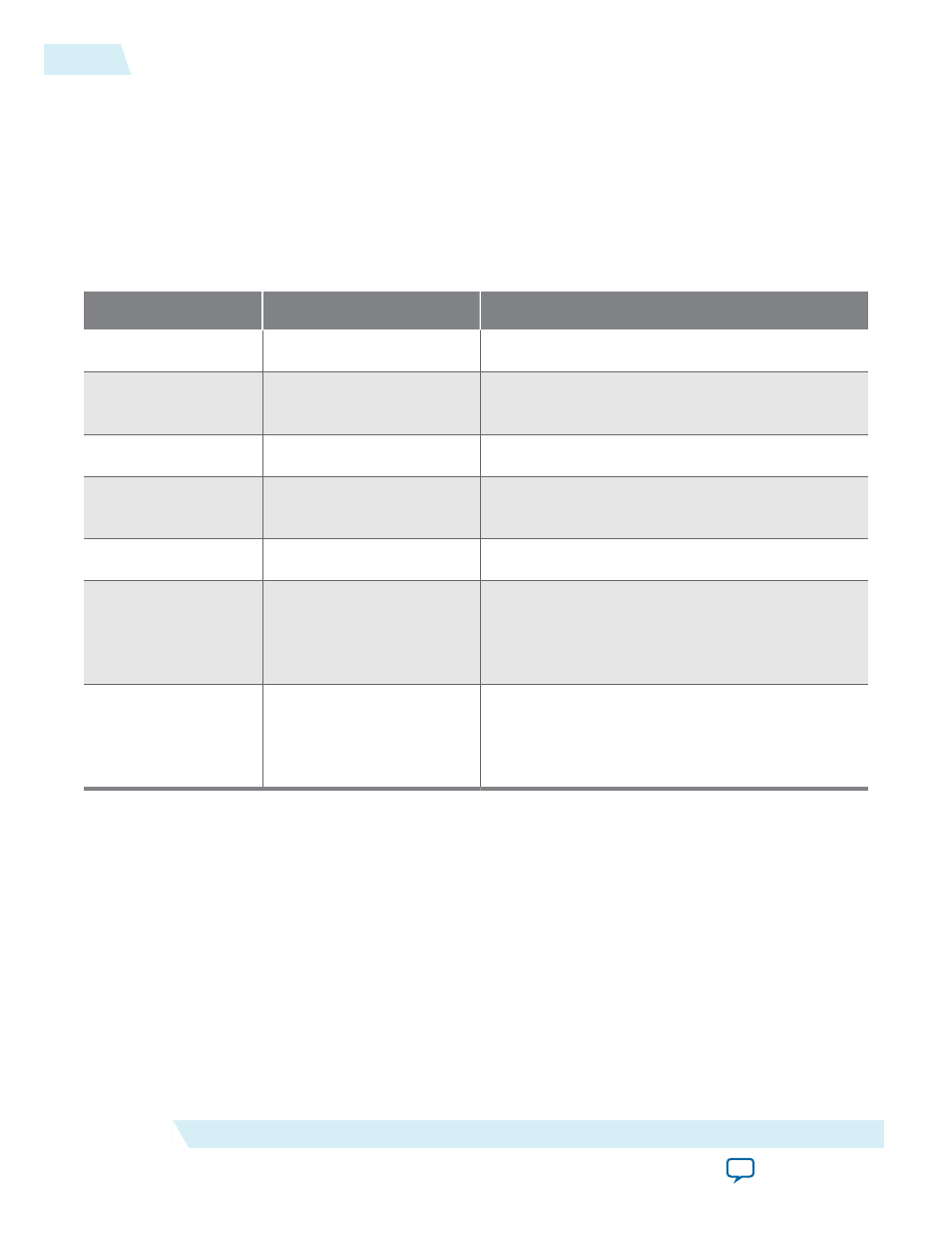

Table 5-13: Connecting CVI Signals to DisplayPort Sink Stream 0 Signals

CVI Signal

DisplayPort Sink Signal

Comment

vid_data

rx_vid_data

Video data

vid_datavalid

–

Drive high because the video data is not oversam‐

pled.

vid_f

–

Drive low because the video data is progressive.

vid_locked

rx_vid_locked

The core asserts this signal when a stable stream is

present.

vid_de

rx_vid_valid

Indicates the active picture region of a line.

vid_h_sync

rx_vid_eol

The

rx_vid_eol

signal generates the

vid_h_sync

pulse by delaying it (by 1 clock cycle) to appear in

the horizontal blanking period after the active

video ends (

rx_vid_valid

is deasserted).

vid_v_sync

rx_vid_eof

The

rx_vid_eof

signal generates the

vid_v_sync

pulse by delaying it (by 1 clock cycle) to appear in

the vertical blanking period after the active video

ends (

rx_vid_valid

is deasserted).

Example 5-1: Verilog HDL CVI — DisplayPort Sink Example

// CVI V-sync and H-sync are derived from delayed versions of the eol and eof signals

always @ (posedge clk_video)

begin

rx_vid_h_sync <= rx_vid_eol;

rx_vid_v_sync <= rx_vid_eof;

end

assign vid_data = rx_vid_data;

assign vid_datavalid = 1’b1;

assign vid_f = 1’b0;

assign vid_locked = rx_vid_locked;

5-18

Clocked Video Input Interface

UG-01131

2015.05.04

Altera Corporation

DisplayPort Sink