Altera DisplayPort MegaCore Function User Manual

Page 25

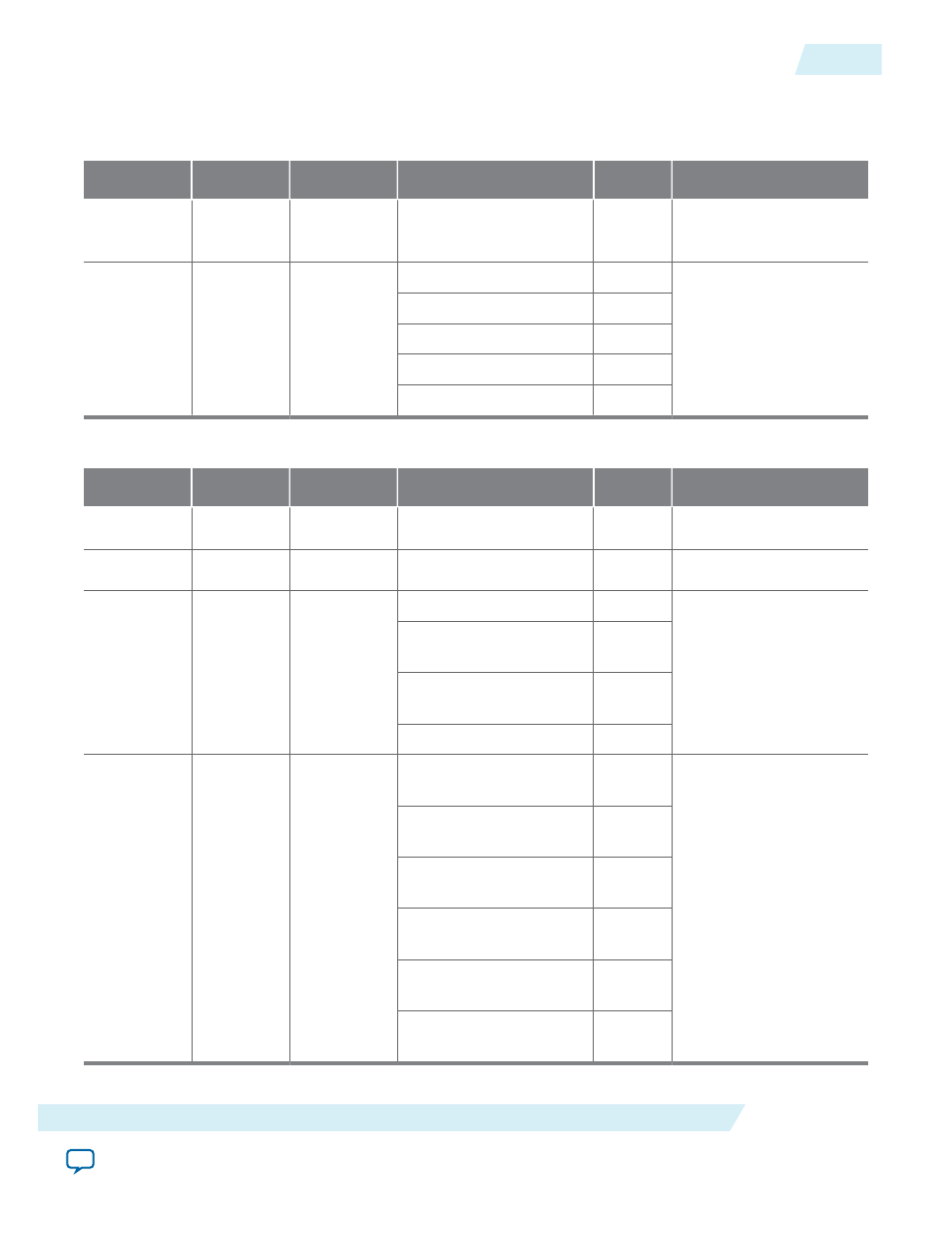

Table 4-4: Video Interface

v

is the number of bits per color, p is the pixels per clock (1 = single, 2 = dual, and 4 = quad).

N

is the stream

number; for example,

tx_vid_clk

represents Stream 0,

tx1_vid_clk

represents Stream 1, and so on.

Interface

Port Type

Clock Domain

Port

Direction

Description

txN_vid_

clk

Clock

N/A

txN_vid_clk

Input

Video clock

txN_

video_in

Conduit

txN_vid_clk

txN_vid_data[3v*p-1:0]

Input

Video data and

standard H/V synchro‐

nization video port

input

txN_vid_v_sync[p-1:0]

Input

txN_vid_h_sync[p-1:0]

Input

txN_vid_f[p-1:0]

Input

txN_vid_de[p-1:0]

Input

Table 4-5: AUX Interface

Interface

Port Type

Clock Domain

Port

Direction

Description

aux_clk

Clock

N/A

aux_clk

Input

AUX channel clock

aux_reset Reset

aux_clk

aux_reset

Input

AUX channel reset

tx_aux

Conduit

aux_clk

tx_aux_in

Input

AUX channel interface

tx_aux_out

Outp

ut

tx_aux_oe

Outp

ut

tx_hpd

Input

tx_aux_

debug

AV-ST

aux_clk

tx_aux_debug_

data[31:0]

Output

Avalon-ST stream of

AUX data for

debugging

tx_aux_debug_valid

Outp

ut

tx_aux_debug_sop

Outp

ut

tx_aux_debug_eop

Outp

ut

tx_aux_debug_err

Outp

ut

tx_aux_debug_cha

Outp

ut

UG-01131

2015.05.04

Source Interfaces

4-9

DisplayPort Source

Altera Corporation