Altera HyperTransport MegaCore Function User Manual

Page 52

3–26

Chapter 3: Specifications

HyperTransport MegaCore Function Specification

HyperTransport MegaCore Function User Guide

© November 2009

Altera Corporation

Preliminary

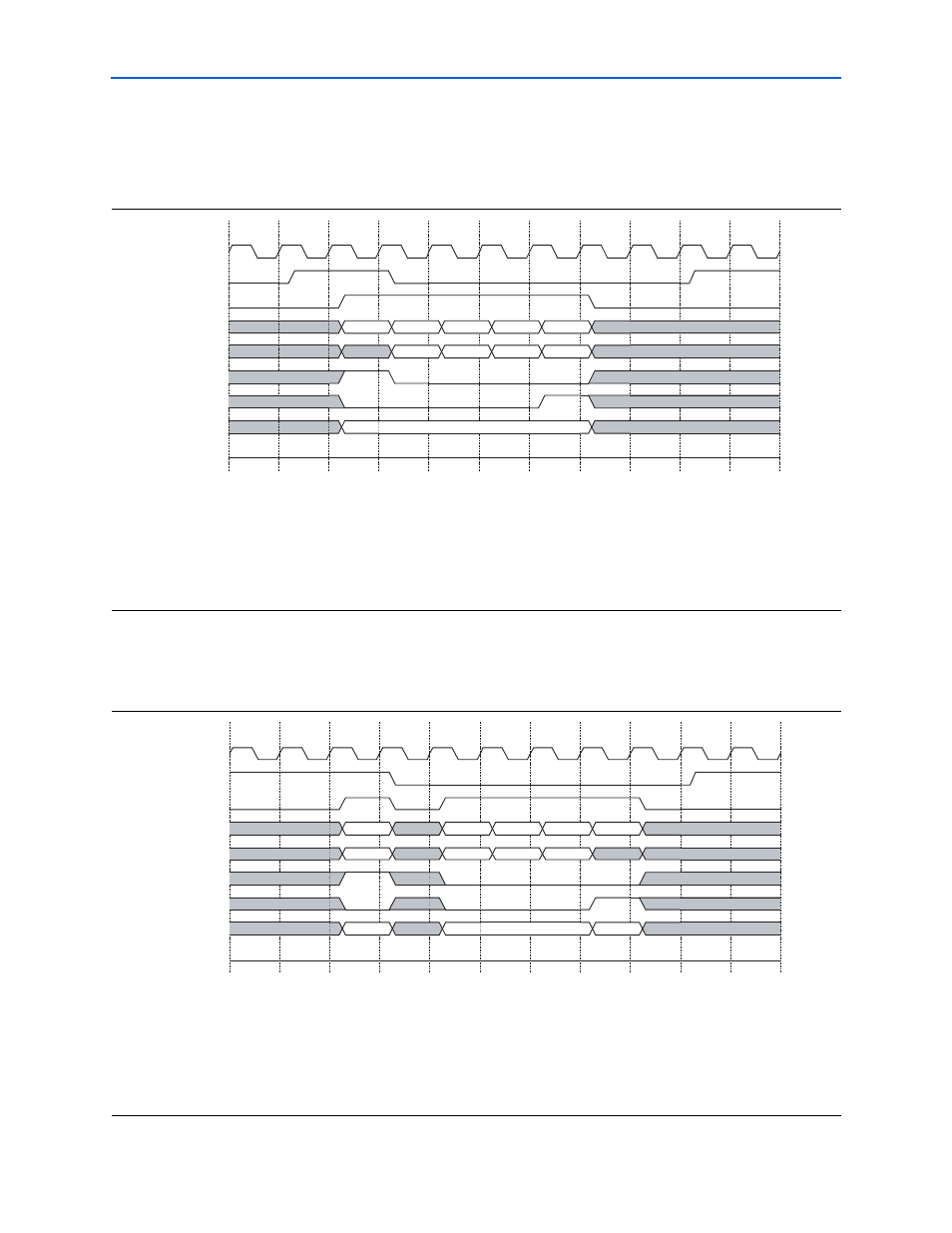

Tx Command/Data Buffer Interface Timing Diagrams

shows a 32-byte read response being transferred to the HyperTransport

MegaCore function across the Tx interface.

shows a 28-byte write being transferred to the HyperTransport MegaCore

function across the Tx Interface. The user logic inserts a wait state during the transfer.

Figure 3–14. Single 32-Byte Read Response across Tx Interface, No Wait States Timing Diagram

Notes to

:

(1) In this example,

Dav_o

starts out low. The clock cycle after

Dav_o

is asserted, the user application asserts

DatEna_i

. In other cases,

Dav_o

may be high for many clock cycles and the user application does not assert

DatEna_i

until it has data available.

(2)

Dav_o

goes low in this example to indicate the TxResp buffer is full and cannot accept a subsequent command. However, the user application

still asserts

DatEna_i

to complete the current command.

(3) Some time later

Dav_o

is reasserted, indicating another command can be accepted.

(4)

Dat_o[63:32]

is not valid in this example because the command is only a read response.

2

3

4

5

6

7

9

10

RefClk

Dav_o

8

1

DatEna_i

Dat_i[31:0]

Dat_i[63:32]

Sop_i

Eop_i

WrRjct_o

Mty_i[2:0]

11

RdResp

DW0

DW2

DW4

DW6

DW1

DW3

DW5

DW7

0b000

(2)

(3)

(4)

(1)

Figure 3–15. User Wait States on the Tx Interface Timing Diagram

Notes to

:

(1) In this example,

Dav_o

is high for many clock cycles and the user application asserts

DatEna_i

when it has data available.

(2)

Dav_o

goes low in this example to indicate the TxResp buffer is full and cannot accept a subsequent command. However, the user application

still asserts

DatEna_i

to complete the current command.

(3) Some time later Dav_o is reasserted, indicating another command can be accepted.

(4) The user inserts a wait state in the transfer by deasserting

DatEna_i

; the other inputs are Don’t Cares in this clock cycle.

(5)

Dat_i[63:32]

is not valid because this example is only seven double-words.

2

3

4

5

6

7

9

10

RefClk

Dav_o

8

1

DatEna_i

Dat_i[31:0]

Dat_i[63:32]

Sop_i

Eop_i

WrRjct_o

Mty_i[2:0]

11

(1)

Write

DW0

DW2

DW4

DW6

DW1

DW3

DW5

(5)

0b000

(2)

(3)

Addr[39:8]

(4)

(4)

0b100

(4)

(4)

(4)

0b000

(4)