Altera HyperTransport MegaCore Function User Manual

Page 61

Chapter 3: Specifications

3–35

HyperTransport MegaCore Function Specification

© November 2009

Altera Corporation

HyperTransport MegaCore Function User Guide

Preliminary

Link Control Registers (Actual Offsets 0x44, 0x48)

The HyperTransport MegaCore function cannot be software configured. The user

must assume that link zero is connected to the host bridge. Additionally, link 1 is

connected to the device end chain. The bits of link control 0 register are described in

the following table. The link control one register is hardwired to 0x0050, indicating

that the device is an end-chain device.

describes the HT capability link

control registers.

Link Configuration Registers (Actual Offsets 0x46, 0x4A)

There are two link configuration registers in every device, one for each link. The

unused register for the unused link is reserved. The HyperTransport MegaCore

function always uses link configuration register 0 in the case of an end-chain

instantiation.

describes the HT capability link configuration registers.

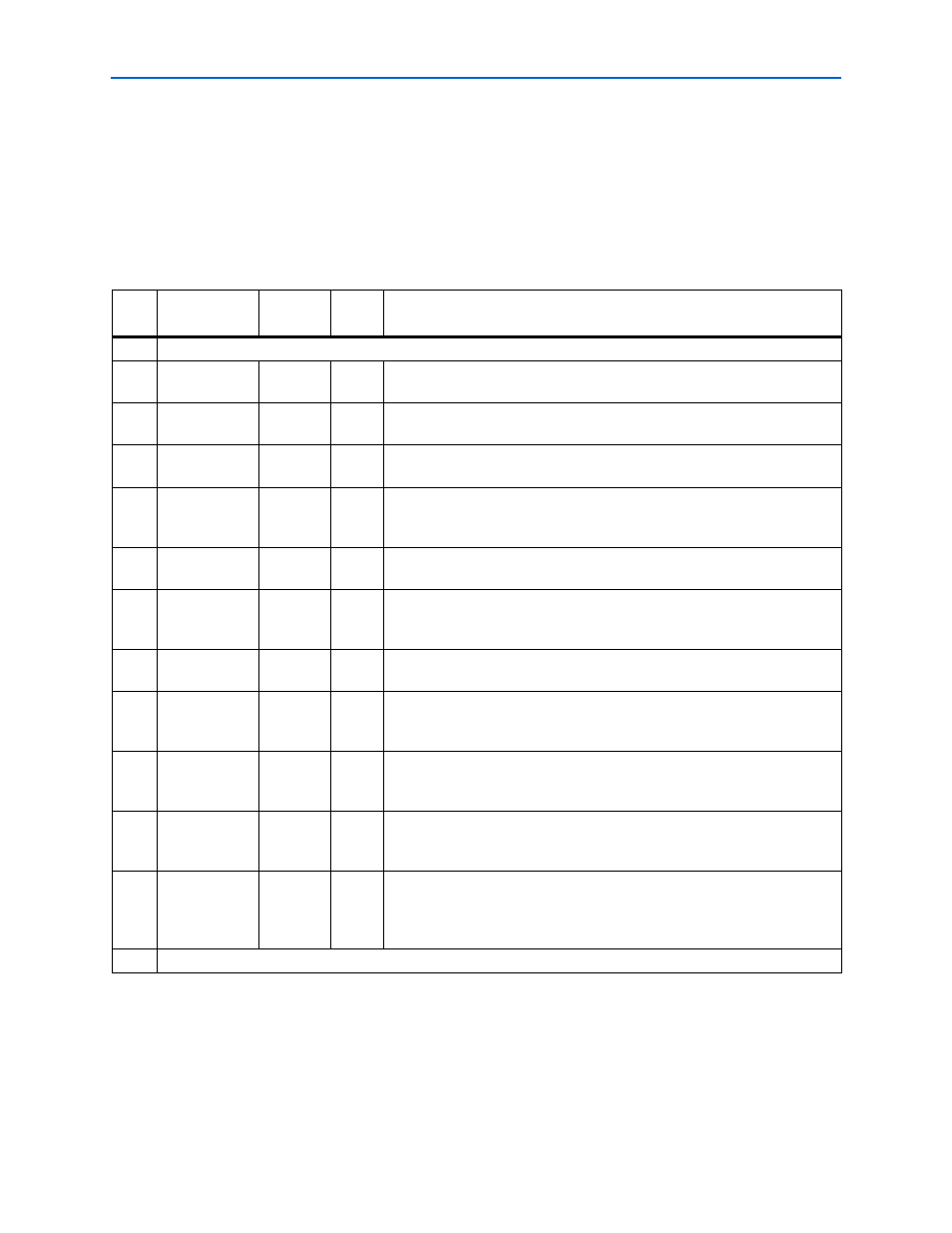

Table 3–17. HT Capability Link Control Register Bits Offset: Capability Pointer + 0x04 (Actual Offset: 0x44)

Bits

Name

Register

Type

Reset

Used

Description

0

Reserved

1

CRC Flood

Enable

R/W

Warm

The link generates a sync flood error if this bit is set. Otherwise, the CRC

checker logs the errors.

2

CRC Start Test

HW to 0

N/A

The HyperTransport MegaCore function does not support the CRC test

sequence. This bit is hardwired to zero.

3

CRC Force

Error

R/O

N/A

This bit forces bad CRC generation. The HyperTransport MegaCore function

does not support this mode.

4

Link Failure

R/C

Cold

Set this bit when a failure is detected and causes a sync flood. These errors

include CRC, protocol error, or overflow error. This bit is hardwired to one for

end-chain applications.

5

Initialization

Complete

R/O

Warm

Set to 1 automatically when the low-level initialization is complete.

6

End of Chain

R/O

Warm

Indicates that a link is not part of the logical HT chain. This bit is

parameterized. Link zero always has its bit hardwired to zero; link one is

hardwired to one.

7

Transmitter Off

R/O

N/A

Allows shutting down the transmitter. When this bit is set, outputs do not

toggle. This bit is hardwired to zero.

11:8

CRC Error

R/C

Cold

One of these bits is set when a CRC error is detected. Errors are detected and

reported on per byte basis. Because the 8-bit HyperTransport MegaCore

function only implements one byte, bits 11,10, and 9 are hardwired to 0.

12

Isoc Enable

R/O

N/A

Controls whether the isochronous flow control mode is supported or not.

Because the HyperTransport MegaCore function does not support the

isochronous flow control mode, this bit is hardwired to zero.

13

LDTSTOP#

Tristate Enable

R/O

N/A

Controls whether the link tristates the signals during a disconnect state of

LDTSTOP# sequence. Because the HyperTransport MegaCore function does

not support power management, this bit is hardwired to 0.

14

Extended CTL

Time

R/O

N/A

If this bit is set during the initialization sequence, CTL is asserted for 50

s

after the point where both Tx and Rx assert CTL. The MegaCore function only

supports the 16-bit time after both Tx and Rx assert CTL, therefore, this bit is

hardwired to zero.

15

Reserved